## UNIVERSITÄT DER BUNDESWEHR MÜNCHEN Fakultät für Elektrotechnik und Informationstechnik

# Ladungsspeicherung in Oxid-Nitrid-Oxid (ONO) Strukturen für nichtflüchtige Speicherbauelemente

Jan-Malte Schley jm.schley@gmx.de

Vorsitzender des Promotionsausschusses: Prof. Dr.-Ing. H. Baumgärtner

1.Berichterstatter: Prof. Dr.-Ing. K. Hoffmann

2.Berichterstatter: Prof. Dr. rer. nat. I. Eisele

Tag der Prüfung: 2. März 2005

Mit der Promotion erlangter akademischer Grad:

Doktor-Ingenieur

(Dr.-Ing.)

Dresden, den 18. März 2005

### Vorwort und Danksagung

Die vorliegende Arbeit entstand begleitend zu meiner Tätigkeit als Entwicklungsingenieur der Firma Infineon Technologies im Bereich der Technologieentwicklung.

Ganz herzlich bedanken möchte ich mich bei Herrn Prof. Dr.-Ing. K. Hoffmann, der mir diese externe Arbeit am Institut für Elektronik der Universität der Bundeswehr München ermöglicht hat.

Sehr dankbar bin ich Herrn Prof. Hoffmann auch für seine vielen wertvollen Anregungen, seinen begeisternden Optimismus und die Freiheiten, die er mir bei der Ausgestaltung des Themas ließ.

Zu großem Dank bin ich auch meinem Vorgesetzten bei Infineon Technologies Herrn Dr. C. Ludwig verpflichtet, er hat durch seine stetige Unterstützung wesentlich zum Gelingen dieser Arbeit beigetragen.

Weiterhin möchte ich mich bei allen meinen Kollegen von Infineon Technologies bedanken, die mich bei dieser Arbeit unterstützt haben. Mein besonderer Dank gilt Dr. T. Mikolajick und Dr. T. Kern.

Mein ganz besonderer Dank für so unglaublich Vieles gebührt Inka.

## Patentanmeldungen und

## Veröffentlichungen

veröffentlichte Patentanmeldung:

Method for efficient carrier generation in silicon waveguide systems for switching/modulating purposes using parallel pump and signal waveguides (United States Patent and Trademark Office, application No.: 20040114847)

Als Teil der Technologieentwicklung bei Infineon wurden zu folgenden Veröffentlichungen Beiträge geleistet:

Willer et al., 110nm NROM Technology for Code and Data Flash Products, IEEE VLSI 2004

Mikolajick et al., Optimisation of a Multi-Bit Charge Trapping Memory Cell using Process/Device Simulation, IEEE Non-Volatile Semiconductor Workshop 2004

Hagenbeck et al., Modeling and Simulation of Electron Injection during Programming in  $TwinFlash^{TM}$  Devices Based on Energy Transport and Non-Local Lucky Electron Concept, International Workshop on Computational Electronics 2004

## Inhaltsverzeichnis

| V            | orwo   | rt und  | l Danksagung                            | 111      | L |

|--------------|--------|---------|-----------------------------------------|----------|---|

| Pa           | atent  | anmel   | dungen und Veröffentlichungen           | V        | 7 |

| $\mathbf{A}$ | bbild  | lungsv  | rerzeichnis                             | X        | _ |

| Ta           | abelle | enverz  | eichnis                                 | XIV      | 7 |

| Li           | ste d  | ler ver | rwendeten Formelzeichen und Abkürzungen | XV       | 7 |

| 1            | Ein    | leitung | g                                       | 1        | L |

|              | 1.1    | Motiv   | vation für NROM                         | <br>. 1  | Ĺ |

|              | 1.2    | Aufba   | au der Arbeit                           | <br>. 2  | 2 |

| <b>2</b>     | Gru    | ındlag  | en                                      | 4        | 1 |

|              | 2.1    | MOS-    | -Struktur                               | <br>. 4  | 1 |

|              | 2.2    | MOS-    | -Transistor                             | <br>. 10 | ) |

|              | 2.3    | MOS-    | -Transistor im sub $\mu m$ - Bereich    | <br>. 13 | 3 |

|              |        | 2.3.1   | Kanallängenmodulation                   | <br>. 13 | 3 |

|              |        | 2.3.2   | Ladungsträgerbeweglichkeit              | <br>. 17 | 7 |

|              |        | 2.3.3   | Kurzkanaleffekt                         | <br>. 19 | ) |

|              |        | 2.3.4   | Schmalkanaleffekt                       | <br>. 22 | 2 |

|              |        | 2.3.5   | Heiße Elektronen                        | <br>. 26 | 3 |

|              |        | 2.3.6   | Diodendurchbruch und Punchthrough       | . 28     | 3 |

|   |      | 2.3.7  | Subthreshold swing                                                  | 29 |

|---|------|--------|---------------------------------------------------------------------|----|

|   | 2.4  | NRON   | M-Speicherzelle                                                     | 31 |

|   |      | 2.4.1  | Schreiben, Lesen und Löschen                                        | 32 |

| 3 | Zell | konzep | ote und Modellbildung                                               | 35 |

|   | 3.1  | Konve  | entionelles Konzept (C-Konzept)                                     | 36 |

|   | 3.2  | STI-K  | onzept                                                              | 41 |

|   | 3.3  | Tabell | arischer Vergleich von C- und STI-Konzept                           | 47 |

|   | 3.4  | Model  | lbildung für NROM-Speicherzellen                                    | 48 |

|   |      | 3.4.1  | Programmieren und Löschen im Bändermodell                           | 49 |

|   |      | 3.4.2  | Traps und Ladungstransport in Siliziumnitrid                        | 51 |

|   |      | 3.4.3  | Ladungsverlust durch thermische Emission von Ladungsträgern    .  . | 58 |

|   |      | 3.4.4  | Ladungsverlust in vertikaler Richtung                               | 59 |

|   |      | 3.4.5  | Ladungsverlust durch laterale Bewegung von Löchern                  | 59 |

|   |      | 3.4.6  | Zwei-Transistor-Modell für eine programmierte NROM-Zelle $$         | 65 |

| 4 | Exp  | erime  | ntelle Evaluierung des                                              |    |

|   | STI  | - Kon  | nzepts                                                              | 73 |

|   | 4.1  | Einsat | zspannungen und Transferkennlinien                                  | 73 |

|   | 4.2  | Kanal  | dotierung                                                           | 76 |

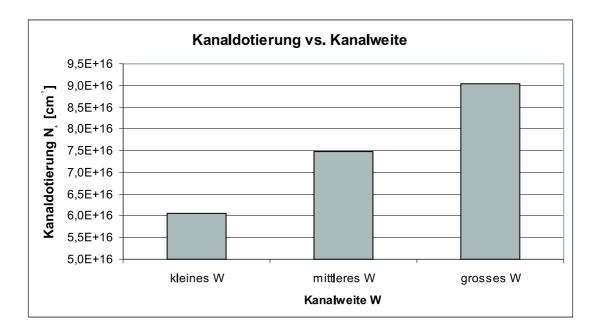

|   |      | 4.2.1  | Weiten-Effekt                                                       | 79 |

|   | 4.3  | Progra | ammierkurven                                                        | 79 |

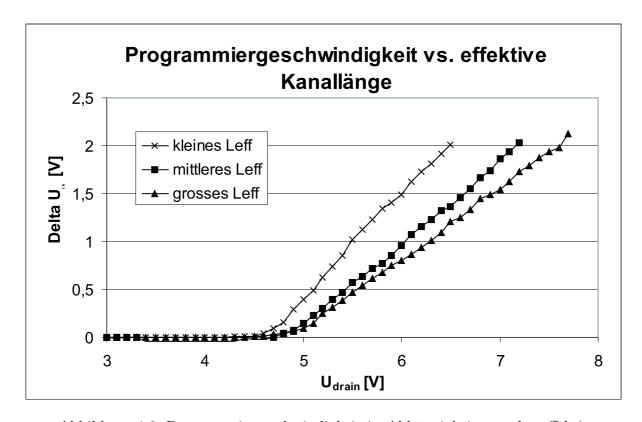

|   |      | 4.3.1  | Längen-Effekt                                                       | 80 |

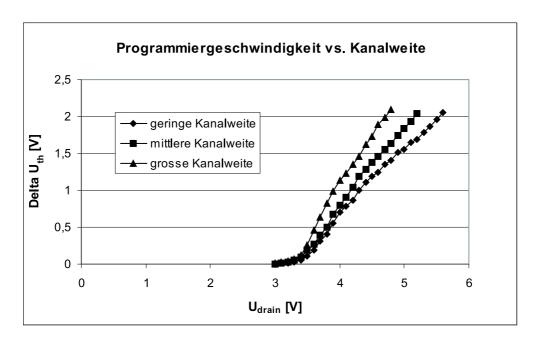

|   |      | 4.3.2  | Weiten-Effekt                                                       | 82 |

|   | 4.4  | Löschl | kurven                                                              | 83 |

|   |      | 4.4.1  | Längen-Effekt                                                       | 84 |

|   | 4.5  | Neben  | sprechen                                                            | 86 |

|   |      | 4.5.1  | Position bzw. Breite der eingeschossenen Ladungsverteilungen im ONC | 87 |

|   |      | 4.5.2  | Kanaldotierung                                                      | 88 |

| IN       | 'HAL' | ΓSVERZEICHNIS                                  | IX  |

|----------|-------|------------------------------------------------|-----|

|          |       | 4.5.3 Effektive Kanallänge                     | 92  |

|          |       | 4.5.4 Kanalweite                               | 92  |

|          | 4.6   | Punch-Messungen                                | 94  |

|          | 4.7   | Zyklen - Messungen                             | 95  |

|          |       | 4.7.1 Vergleich der Degradation nach Zyklen    | 99  |

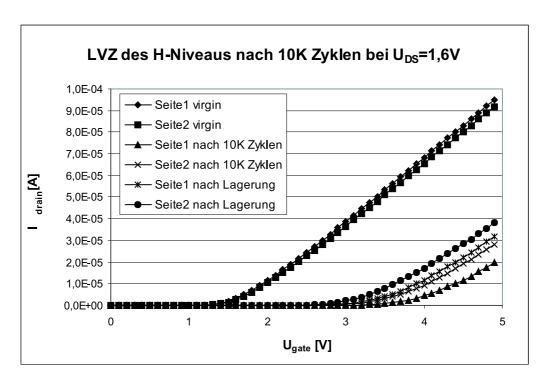

|          | 4.8   | LVZ - Ladungsverlust nach Zykeln               | 101 |

|          | 4.9   | Beweglichkeit von Ladungsträgern im ONO        | 104 |

|          | 4.10  | Temperaturabhängigkeit von NROM-Zellen         | 107 |

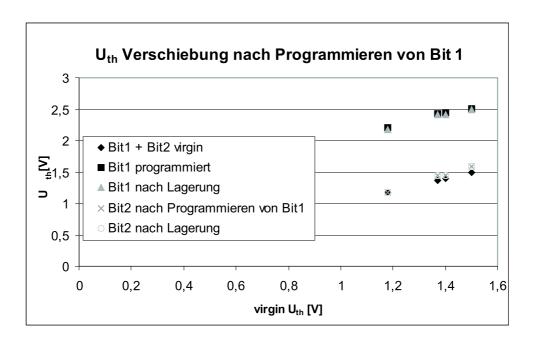

| 5        | Mul   | tilevel NROM                                   | 113 |

|          | 5.1   | Herkömmliche Betriebsweise für NROM            | 113 |

|          | 5.2   | Multilevel-Betrieb für NROM                    | 116 |

|          | 5.3   | Experimenteller Vergleich der Betriebsweisen   | 120 |

|          | 5.4   | Multilevel am Beispiel von drei Bits pro Zelle | 123 |

| 6        | Zus   | ammenfassung und Ausblick                      | 127 |

| ${f Li}$ | terat | urverzeichnis                                  | 129 |

## Abbildungsverzeichnis

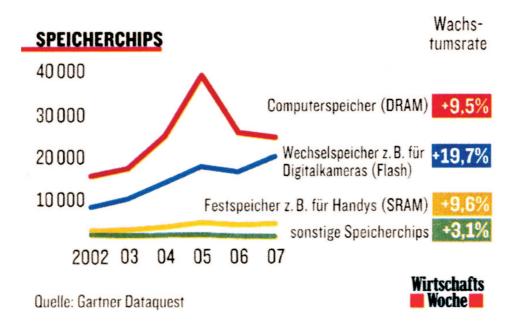

| Wachstumsraten für verschiedene Segmente des Speichermarktes, [11]                          | 2                                                                  |

|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

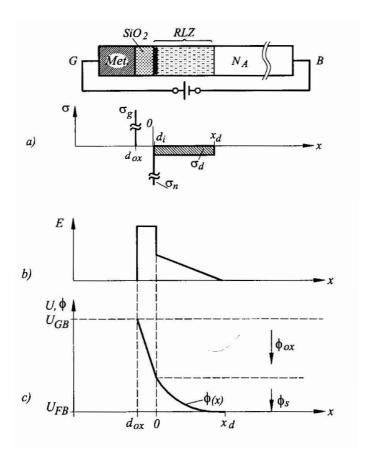

| MOS-Struktur, [24]                                                                          | 5                                                                  |

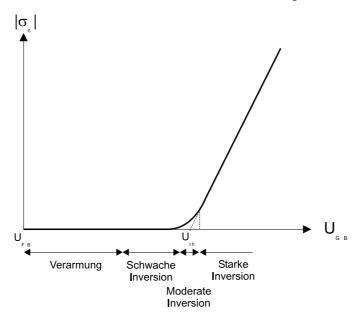

| Betrag der Inversionsschichtladung pro Fläche                                               | 8                                                                  |

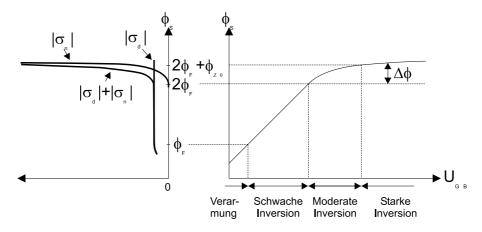

| Oberflächenspannung über Gate-Substrat-Spannung (rechts) und Ladungen                       |                                                                    |

| über Oberflächenspannung (links)                                                            | 9                                                                  |

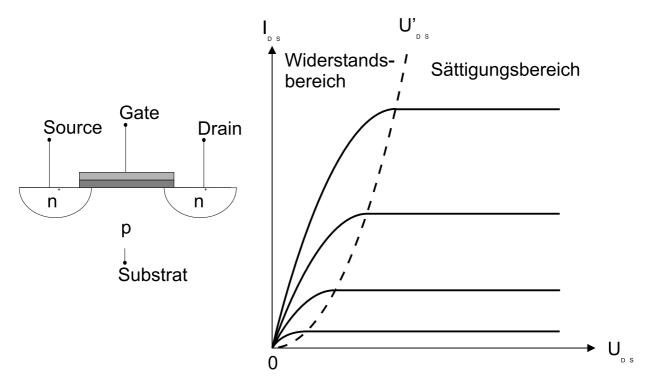

| Schematische Transistordarstellung mit Ausgangskennlinienfeld                               | 10                                                                 |

| Kennlinienfeld unter Einfluss von Kanallängenmodulation                                     | 13                                                                 |

| Schematische Darstellung zur Kanallängenmodulation                                          | 14                                                                 |

| Vereinfachtes Modell zur Kanallängenmodulation                                              | 17                                                                 |

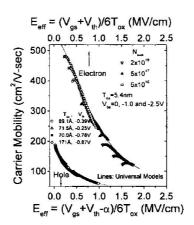

| Modell für die Ladungsträgerbeweglickeit,[8] $\ \ldots \ \ldots \ \ldots \ \ldots \ \ldots$ | 18                                                                 |

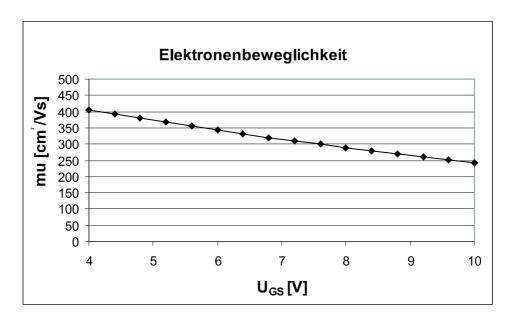

| Elektronenbeweglichkeit als Funktion von $U_{GS}$                                           | 19                                                                 |

| Veranschaulichung des Kurzkanaleffekts, [69]                                                | 20                                                                 |

| Trapezmodell zur Beschreibung des charge-charring bei $U_{DS}=0V,[24].$                     | 20                                                                 |

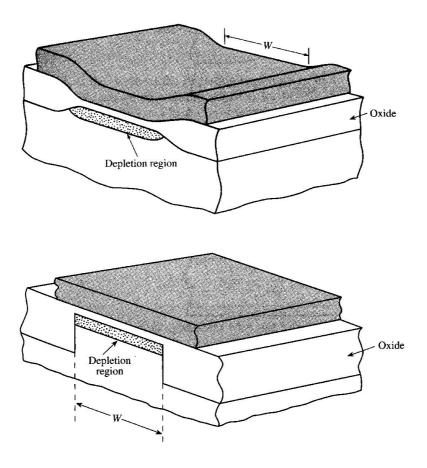

| Querschnitte durch LOCOS/STI Transistoren, [69]                                             | 23                                                                 |

| Weiteneffekt, Auswirkung auf die Einsatzspannung                                            | 24                                                                 |

| Punchtrough-Verhalten                                                                       | 28                                                                 |

| Swing vs. Wannendotierung, [19]                                                             | 31                                                                 |

| Frühe ONO-Speicherzelle, [23]                                                               | 32                                                                 |

| Grundstruktur einer NROM-Speicherzelle                                                      | 33                                                                 |

| Struktur der Zellanordnung im C-Konzept                                                     | 36                                                                 |

|                                                                                             | $\label{eq:moss-struktur} \begin{tabular}{ll} MOS-Struktur, [24] $ |

| 3.2  | Elektrische Zellenfeldarchitektur für das C-Konzept                            | 37 |

|------|--------------------------------------------------------------------------------|----|

| 3.3  | Patent auf Speicherzellen mit einer C-konzeptartigen Architektur, $[70]$       | 38 |

| 3.4  | Längsschnitt (parallel der WL) durch eine NROM-Zelle, $0.17 \mu m$ Technologie | 39 |

| 3.5  | Querschnitt (senkrecht zur WL) durch eine NROM-Zelle, $0.17 \mu m$ Technologie | 40 |

| 3.6  | Struktur der Zellanordnung im STI-Konzept                                      | 41 |

| 3.7  | Struktur der Zellverschaltung im STI-Konzept                                   | 42 |

| 3.8  | Längsschnitt (senkrecht zur WL) durch eine STI begrenzte NROM-Zelle $$ .       | 44 |

| 3.9  | Querschnitt (parallel der WL) durch eine STI begrenzte NROM-Zelle $$           | 45 |

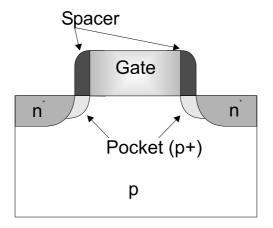

| 3.10 | Schematische Darstellung zum Einsatz von Pocket und Spacer vor Ausdiffusion    | 46 |

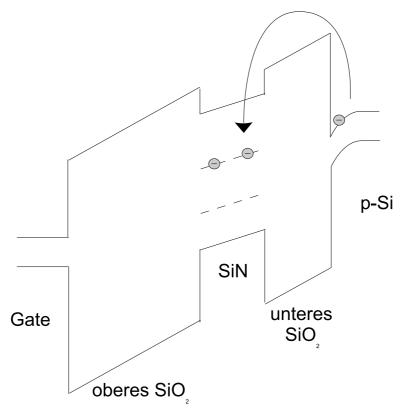

| 3.11 | Schematische Darstellung des Programmierzustands im Bändermodell $ . $ . $ . $ | 50 |

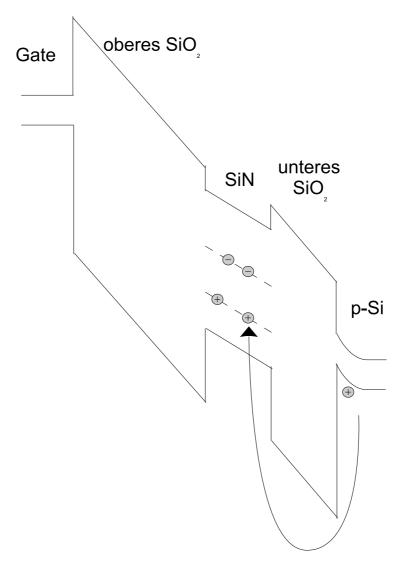

| 3.12 | Schematische Darstellung des Löschzustands im Bändermodell $\ \ldots \ \ldots$ | 51 |

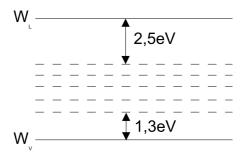

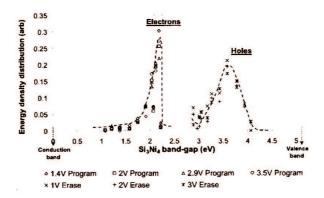

| 3.13 | Fünf wohldefinierte Trap-levels in Siliziumnitrid nach Kapoor, $[32]$          | 52 |

| 3.14 | Trap-Verteilung in der Nitridschicht des ONO, [41]                             | 54 |

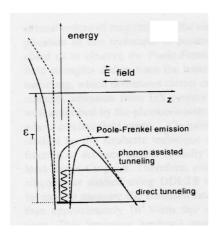

| 3.15 | Potentailbarriere für die Emission von einer geladenen Fangstelle, [17]        | 55 |

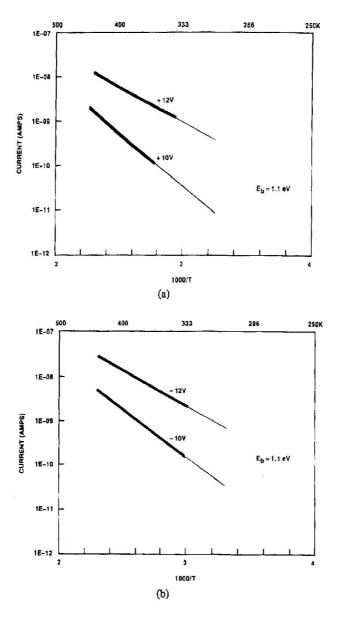

| 3.16 | Temperaturabhängigkeit des Stromes durch eine $25nm$ dicke Siliziumnitrid-     |    |

|      | Schicht, [32]                                                                  | 57 |

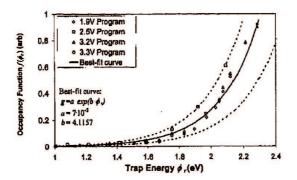

| 3.17 | Trap-Besetzung als Funktion der Energie, [44]                                  | 58 |

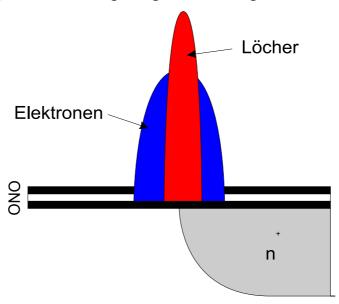

| 3.18 | Schematische Darstellung der Ladungsträgerverteilungen im ONO                  | 61 |

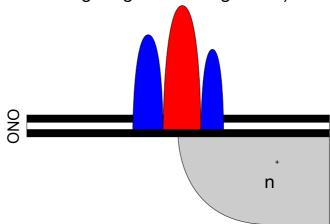

| 3.19 | Einsatzspannungsentwicklung beim Zykeln einer NROM-Zelle mit konstan-          |    |

|      | ten Programmier- und Löschbedingungen                                          | 66 |

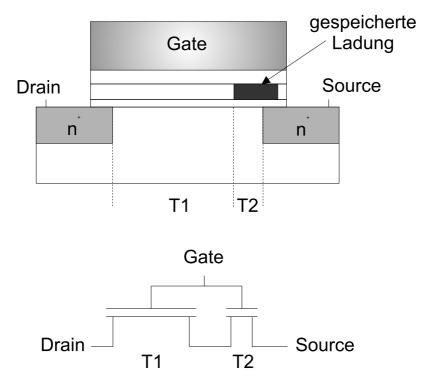

| 3.20 | Schematische Darstellung einer programmierten NROM-Zelle und ihrer Mo-         |    |

|      | dellierung durch zwei Transistoren (T1 und T2)                                 | 67 |

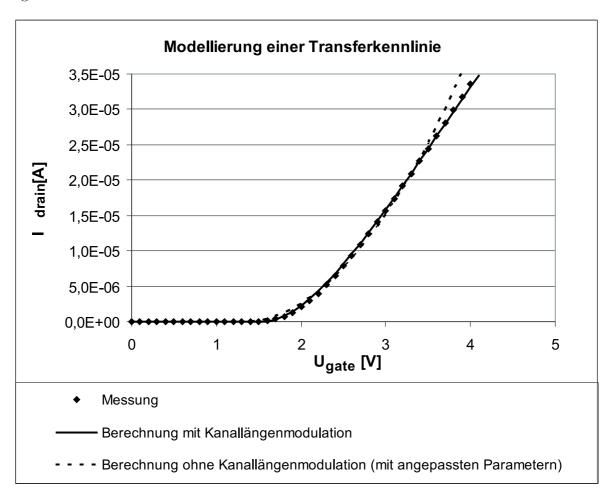

| 3.21 | Gemessene und modellierte Transferkennlinien einer "virgin" NROM-Zelle         | 69 |

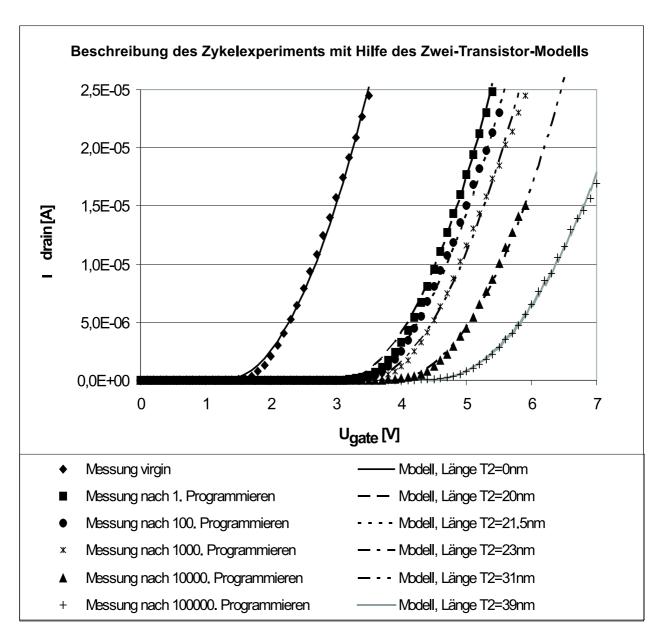

| 3.22 | Modellierung der Entwicklung des programmierten Zustands aus dem in            |    |

|      | Abb. 3.19 dargestellten Versuch durch das Zwei-Transistor-Modell               | 72 |

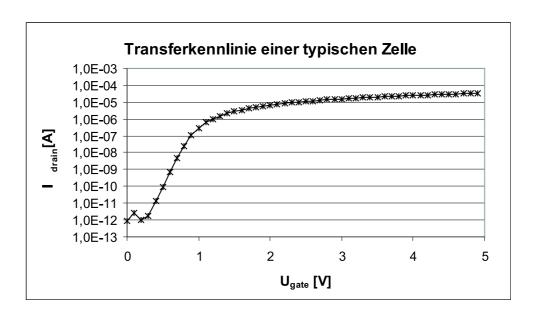

| 4.1  | Transferkennlinie einer typischen STI-begrenzten NROM-Zelle                    | 74 |

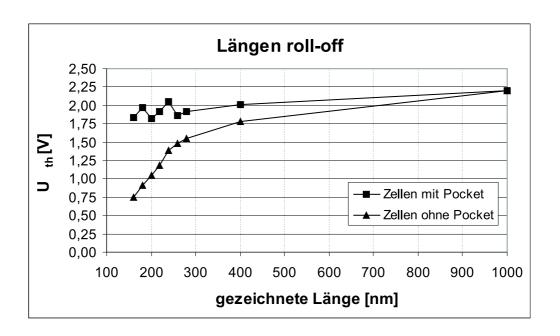

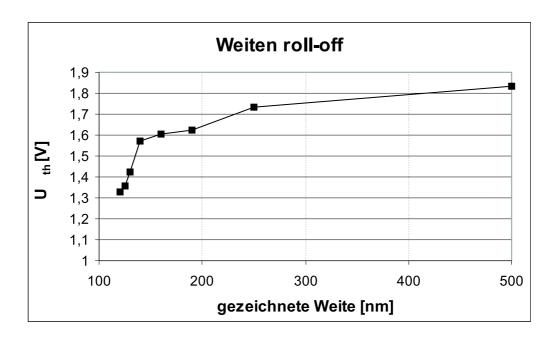

| 4.2  | Längen roll-off                                                                | 75 |

| 4.3  | Weiten roll-off                                                                | 75 |

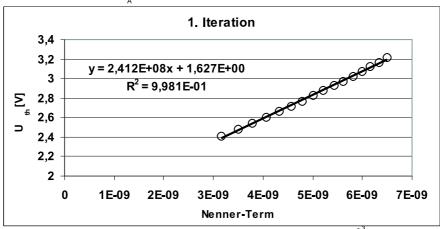

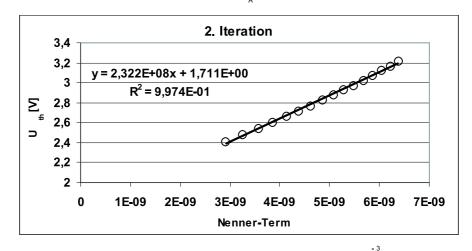

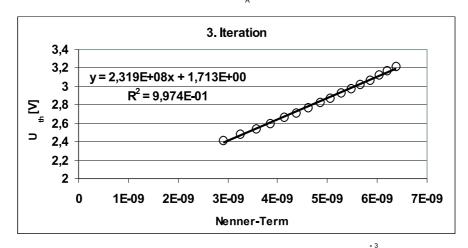

| 4.4  | Iterationsverfahren zur Bestimmung der Kanaldotierung                        | 78  |

|------|------------------------------------------------------------------------------|-----|

| 4.5  | Kanaldotierung vs. Kanalweite                                                | 80  |

| 4.6  | Programmiergeschwindigkeit in Abhängigkeit von der effektiven Kanallänge     | 81  |

| 4.7  | Programmiergeschwindigkeit in Abhängigkeit von der Kanalweite                | 82  |

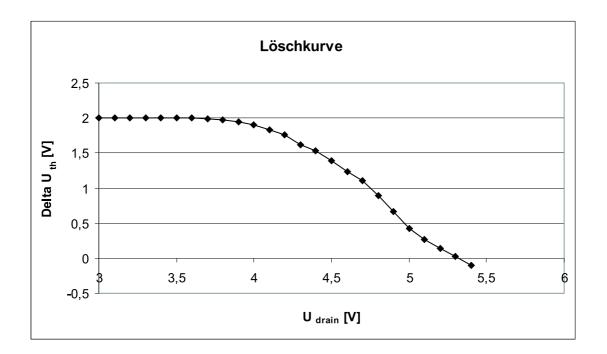

| 4.8  | Relatives Absinken der Einsatzspannung beim Löschen                          | 84  |

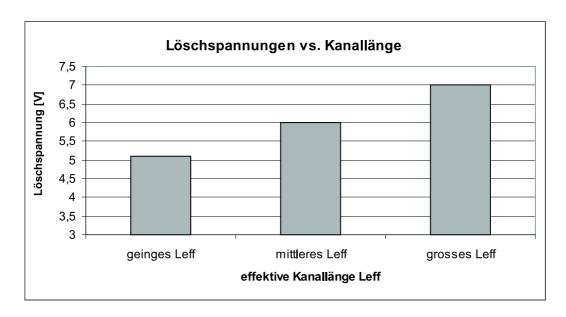

| 4.9  | Löschspannungen in Abhängigkeit von der effektiven Kanallänge                | 85  |

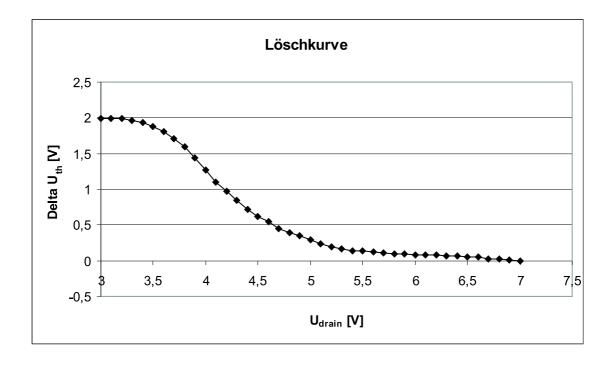

| 4.10 | Löschverlauf einer sehr langen Zelle                                         | 85  |

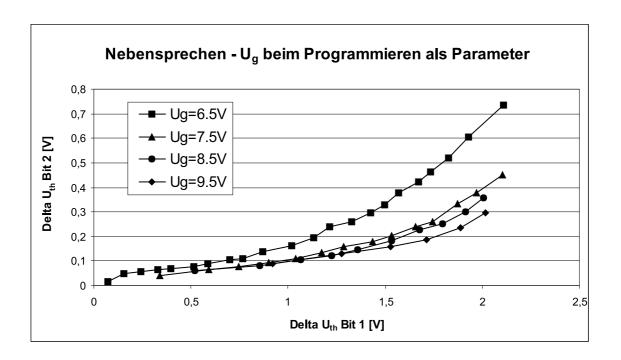

| 4.11 | Nebensprechen - $U_G$ beim Programmieren als Parameter                       | 88  |

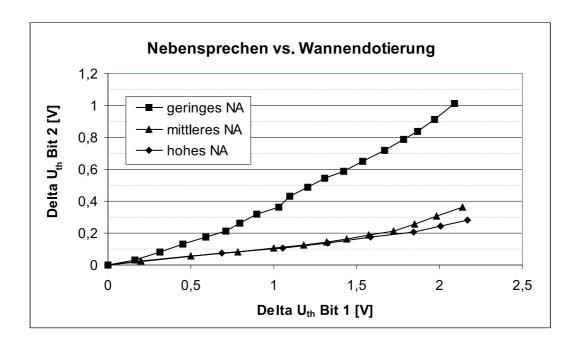

| 4.12 | Nebensprechen vs. Wannendotierung                                            | 89  |

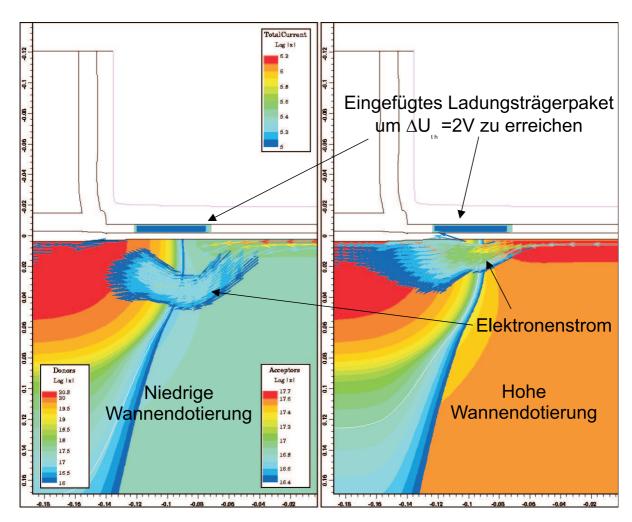

| 4.13 | Simulation der Lesestromverteilung für verschiedene Wannendotierungen, [22]. | 91  |

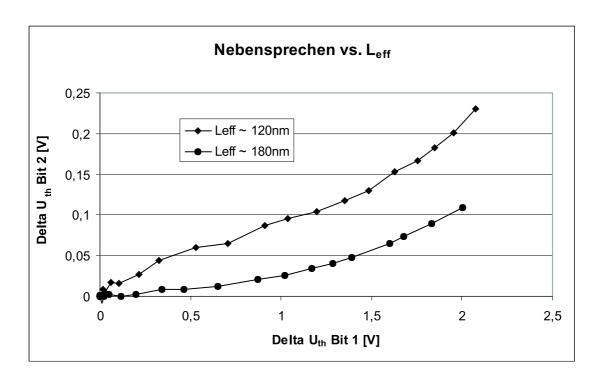

| 4.14 | Nebensprechen vs. effektive Kanallänge                                       | 93  |

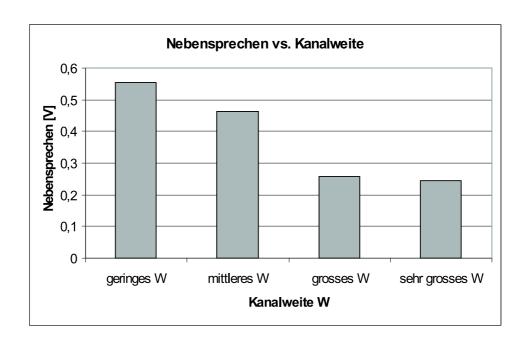

| 4.15 | Nebensprechen vs. Kanalweite                                                 | 93  |

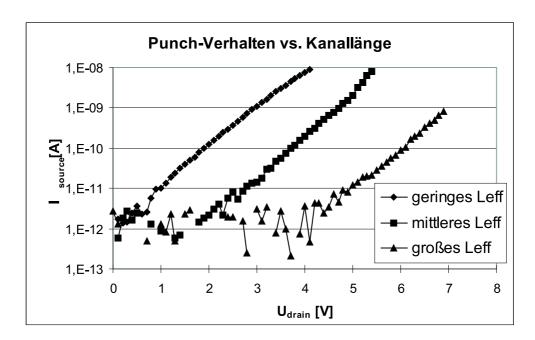

| 4.16 | Punch-Verhalten in Abhängigkeit von der effektiven Kanallänge                | 95  |

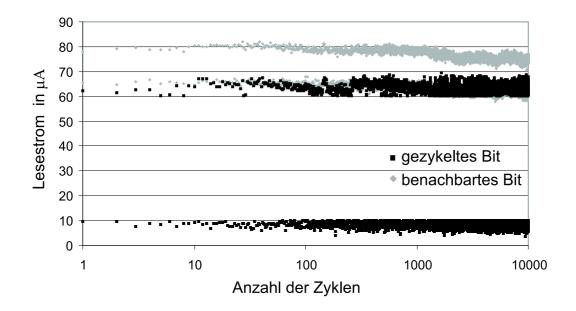

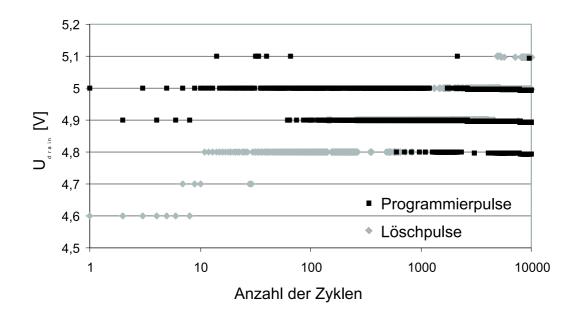

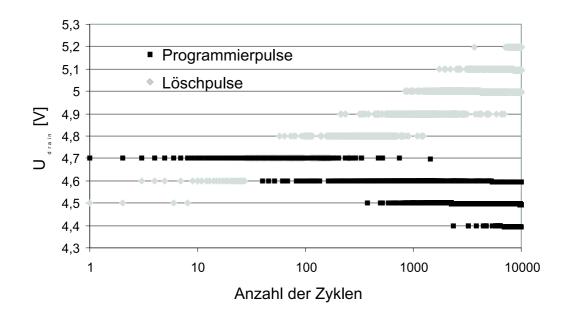

| 4.17 | Zyklen-Messung an einer Zelle mit mittlerer Wannendotierung                  | 97  |

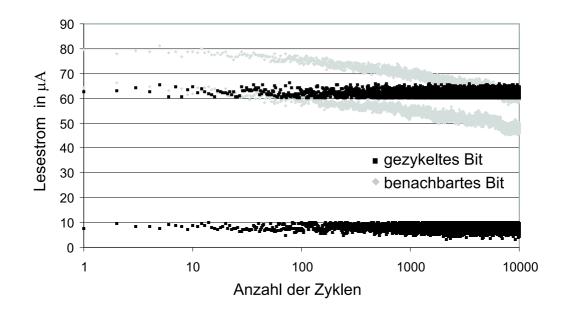

| 4.18 | Zyklen-Messung an einer Zelle mit sehr hoher Wannendotierung                 | 100 |

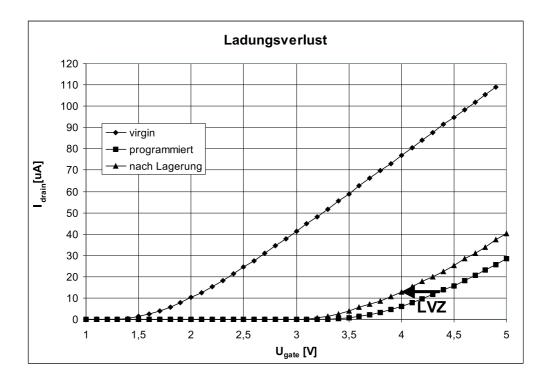

| 4.19 | Ermittlung des Ladungsverlusts                                               | 102 |

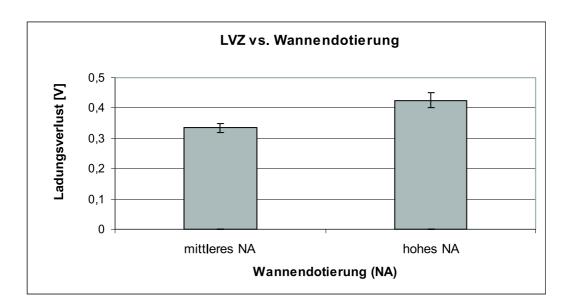

| 4.20 | Ladungsverlust in Abhängigkeit von der Wannendotierung                       | 103 |

| 4.21 | Beweglichkeit von gespeicherten Elektronen                                   | 105 |

| 4.22 | Beweglichkeit von gespeicherten Löchern                                      | 105 |

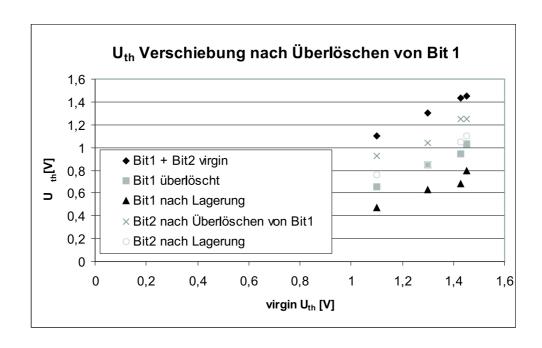

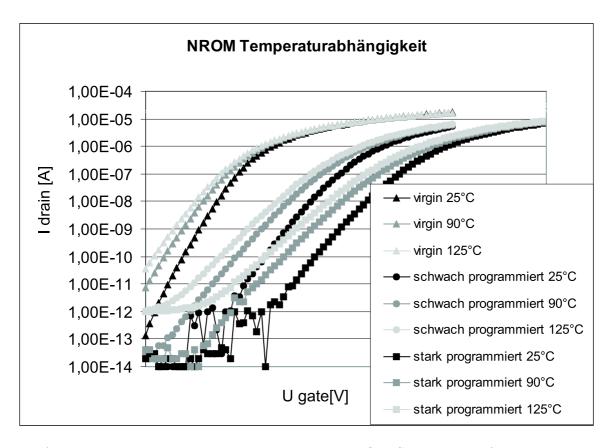

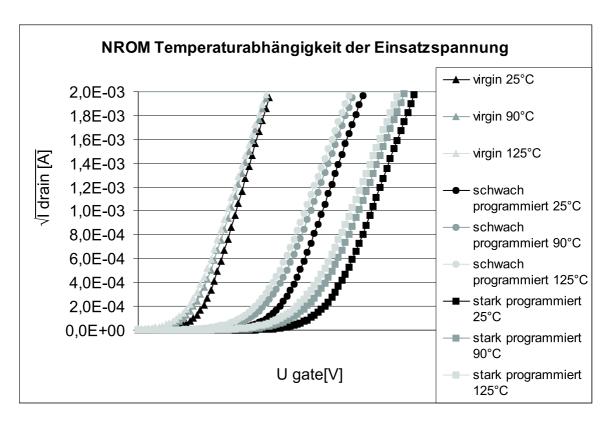

| 4.23 | Temperaturverhalten einer NROM-Speicherzelle                                 | 108 |

| 4.24 | Temperatursensitivität der Einsatzspannung einer NROM-Speicherzelle          | 109 |

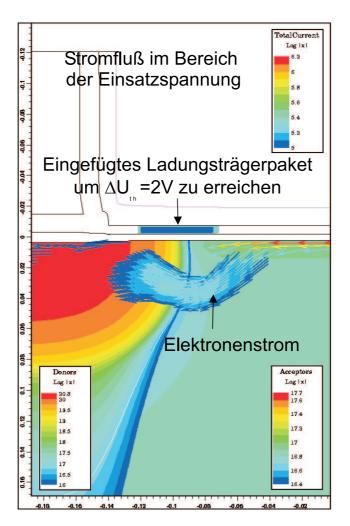

| 4.25 | Simulation der Lesestromverteilung einer programmierten Zelle                | 111 |

| 4.26 | Erklärungsmöglichkeit für die erhöhte Temperaturabhängigkeit von program-    |     |

|      | mierten NROM-Zellen                                                          | 112 |

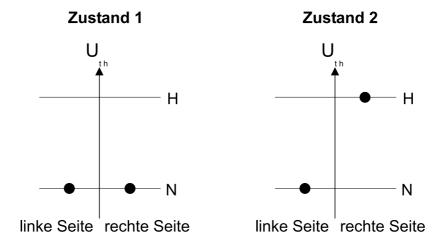

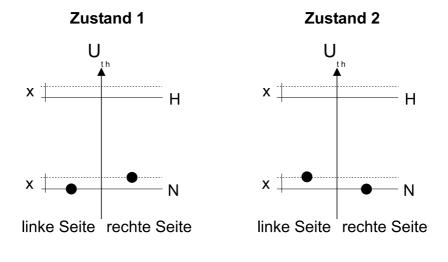

| 5.1  | Gebräuchliche Betriebsweise für zwei Bits pro Zelle bei NROM                 | 114 |

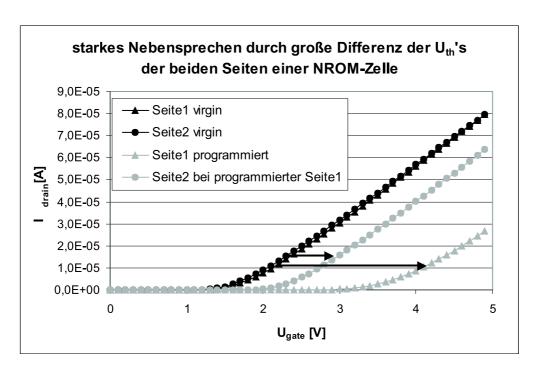

| 5.2  | Auswirkung des Nebensprechens bei der herkömmlichen Betriebsweise für        |     |

|      | NROM                                                                         | 115 |

| 37TTT            |  |

|------------------|--|

| XIII             |  |

| <b>7 7 1 1 1</b> |  |

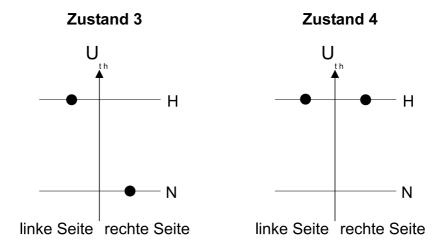

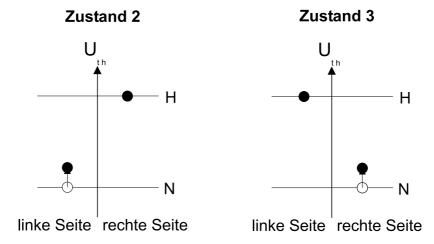

| 5.3 Veranschaulichung des Nebensprechens auf die Zustände $2$ und $3$ aus Abl |                                                                   |     |

|-------------------------------------------------------------------------------|-------------------------------------------------------------------|-----|

|                                                                               | dung 5.1                                                          | 116 |

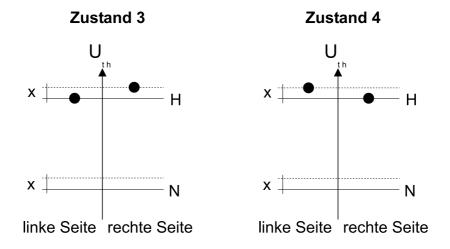

| 5.4                                                                           | Neuer Multilevel-Betrieb für zwei Bits pro Zelle bei NROM         | 117 |

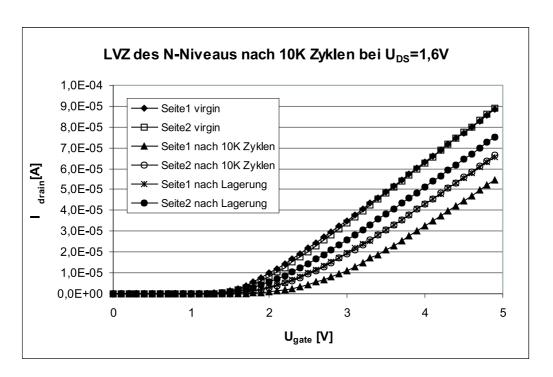

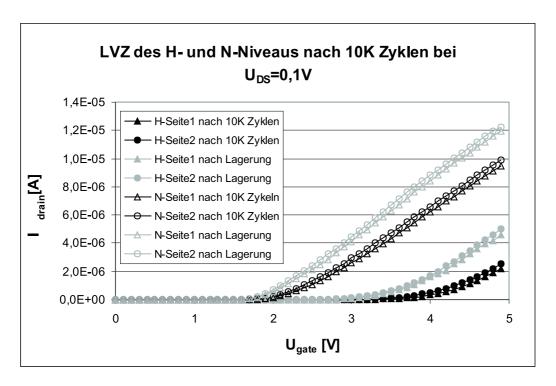

| 5.5                                                                           | LVZ des H-Niveaus bei Multilevel-Betrieb für zwei Bits pro Zelle  | 121 |

| 5.6                                                                           | LVZ des N-Niveaus bei Multilevel-Betrieb für zwei Bits pro Zelle  | 122 |

| 5.7                                                                           | Margin Gain durch zusätzlichen Leseschritt bei niedrigem $U_{DS}$ | 123 |

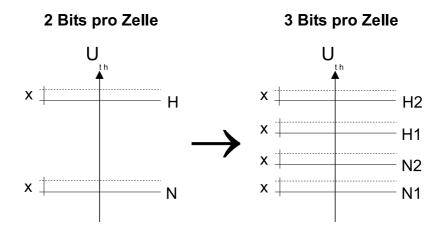

| 5.8                                                                           | Von 2 Bits zu 3 Bits pro Zelle mit Multilevel-Betrieb             | 124 |

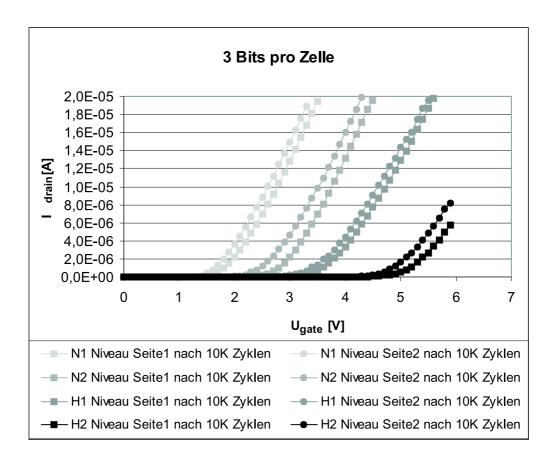

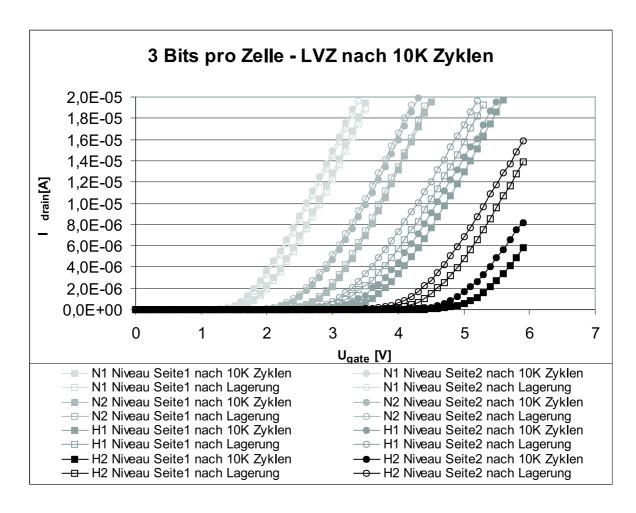

| 5.9                                                                           | Transferkurven für 3 Bits pro Zelle                               | 125 |

| 5.10                                                                          | LVZ bei 3 Bits pro Zelle                                          | 126 |

## Tabellenverzeichnis

| 3.1 | Konzeptvergleich                                      | 48  |

|-----|-------------------------------------------------------|-----|

| 3.2 | Materialparameter für die Darstellung im Bändermodell | 49  |

| 3.3 | Trap-Eigenschaften von Siliziumnitrid                 | 53  |

|     |                                                       |     |

| 4.1 | Iterationsverfahren zur Bestimmung der Kanaldotierung | 77  |

| 4.2 | Nebensprechen vs. Wannendotierung                     | 89  |

| 4.3 | Ergebnisse zur Ladungsträgerbeweglichkeit             | 106 |

| 4.4 | Temperaturabhängigkeit der Einsatzspannung            | 110 |

# Liste der verwendeten Formelzeichen und Abkürzungen

#### Physikalische Konstanten

| Größe           | Bedeutung                                          | Zahlenwert                            |

|-----------------|----------------------------------------------------|---------------------------------------|

| $\epsilon_0$    | Dielektrizitätskonstante des Vakuums               | $8,8542 \cdot 10^{-12} \frac{As}{Vm}$ |

| $\epsilon_{ox}$ | relative Dielektrizitätskonstante von Siliziumoxid | 3,9                                   |

| $\epsilon_{Si}$ | relative Dielektrizitätskonstante von Silizium     | 11, 9                                 |

| k               | Boltzmann-Konstante                                | $1,38 \cdot 10^{-23} \frac{J}{K}$     |

| h               | Plancksches Wirkungsquantum                        | $6.626 \cdot 10^{-34} Js$             |

| q               | Elementarladung                                    | $1,602 \cdot 10^{-19}C$               |

#### Verwendete Bezeichnungen

| Größe     | Bedeutung                                    | Einheit         |

|-----------|----------------------------------------------|-----------------|

| A         | allgemeine Flächenbezeichnung                | $m^2$           |

| $eta_1$   | Anpassungsfaktor für $U_{th}$                | 1               |

| $eta_2$   | Anpassungsfaktor für $U_{th}$                | 1               |

| $C_d'$    | flächenbezogene Kapazität der Verarmungszone | $\frac{F}{m^2}$ |

| $C'_{ox}$ | flächenbezogene Oxidkapazität                | $\frac{F}{m^2}$ |

| D            | elektrische Flussdichte                       | $\frac{C}{m^2}$   |

|--------------|-----------------------------------------------|-------------------|

| $d_{BD}$     | Weite der Verarmungszone an der Drain         | m                 |

| $d_{BS}$     | Weite der Verarmungszone an der Source        | m                 |

| $d_i$        | Dicke der Inversionsschicht                   | m                 |

| $d_{j}$      | Tiefe der Source- bzw. Drain-Gebiete          | m                 |

| $d_{ox}$     | Dicke der Oxidschicht                         | m                 |

| $d_1$        | Korrekturfaktor                               | 1                 |

| $\gamma$     | Substratsteuerfaktor                          | $\sqrt{V}$        |

| E            | elektrische Feldstärke                        | $\frac{V}{m}$     |

| $E_{eff}$    | effektive elektrische Feldstärke              | $\frac{V}{m}$     |

| $E_k$        | kritische elektrische Feldstärke              | $\frac{V}{m}$     |

| $\epsilon_r$ | relative Dielektrizitätskonstante             | 1                 |

| $ u_0$       | attempt-to-escape Frequenz von $SiN$          | $\frac{1}{s}$     |

| $ u_T$       | thermische Emissionsrate                      | $\frac{1}{s}$     |

| $ u_{PF}$    | Poole-Frenkel Emissionsrate                   | $\frac{1}{s}$     |

| $I_{DB}$     | Drain-Bulk-Strom                              | A                 |

| $k_A$        | Propotionalitätsfaktor für die Early-Spannung | $V\sqrt{cm}$      |

| L            | Länge                                         | m                 |

| $L_{Dp}$     | Debye-Länge im p-Gebiet                       | m                 |

| $L_{eff}$    | effektive Kanallänge                          | m                 |

| $l_{km}$     | Strecke zwischen pinch-off und Drain bei      | m                 |

|              | Kanallängenmodulation                         |                   |

| $l_S$        | typische Länge                                | m                 |

| $\lambda_S$  | subthreshold swing Anpassungsfaktor           | 1                 |

| $\mu$        | Ladungsträgerbeweglichkeit                    | $\frac{cm^2}{Vs}$ |

| $\mu_n$      | Elektronenbeweglichkeit                       | $\frac{cm^2}{Vs}$ |

| $N_A$        | Akzeptorendichte                              | $\frac{1}{cm^3}$  |

| $N_C$        | äquivalente Zustandsdichte des Leitungsbands  | $\frac{1}{cm^3}$  |

|              |                                               |                   |

| $N_V$       | äquivalente Zustandsdichte des Valenzbands        | $\frac{1}{cm^3}$   |

|-------------|---------------------------------------------------|--------------------|

| $n_i$       | Intrinsicdichte                                   | $\frac{1}{cm^3}$   |

| n(x)        | Dichte der negativen, beweglichen Ladungsträger   | $\frac{1}{cm^3}$   |

| p(x)        | Dichte der positiven, beweglichen Ladungsträger   | $\frac{1}{cm^3}$   |

| $\phi$      | Potential                                         | V                  |

| $\phi_F$    | Fermispannung                                     | V                  |

| $\phi_i$    | Potential zwischen verschieden dotierten Gebieten | V                  |

| $\phi_{ox}$ | Potentialabfall über $SiO_2$                      | V                  |

| $\phi_K$    | Kontaktspannung                                   | V                  |

| $\phi_r$    | Energie einer Fangstelle                          | eV                 |

| $\phi_S$    | Oberflächenpotential                              | V                  |

| $\phi_t$    | Temperaturspannung                                | V                  |

| Q           | Ladung                                            | C                  |

| ρ           | Raumladungsdichte                                 | $\frac{1}{cm^3}$   |

| S           | subthreshold swing                                | $\frac{V}{Dekade}$ |

| $\sigma_d$  | flächenbezogene Ladung der Raumladungszone        | $\frac{C}{cm^2}$   |

| $\sigma_n$  | flächenbezogene Ladung der Inversionsschicht      | $\frac{C}{cm^2}$   |

| T           | Temperatur                                        | K                  |

| $U_A$       | Early-Spannung                                    | V                  |

| $U_{DB}$    | Drain-Bulk-Spannung                               | V                  |

| $U_{DS}$    | Drain-Source-Spannung                             | V                  |

| $U_{DS}'$   | Drain-Source-Sättigungsspannung                   | V                  |

| $U_{FB}$    | Flachbandspannung                                 | V                  |

| $U_G$       | Gate-Spannung                                     | V                  |

| $U_{GB}$    | Gate-Bulk-Spannung                                | V                  |

| $U_{GS}$    | Gate-Source-Spannung                              | V                  |

| $U_{SB}$    | Source-Bulk-Spannung                              | V                  |

| $U_{th}$    | Einsatzspannung                                   | V                  |

| $v_{e,max}$ | Sättigungsgeschwindigkeit von Elektronen | $\frac{m}{s}$ |

|-------------|------------------------------------------|---------------|

| W           | Weite                                    | m             |

| $W_L$       | min. Energie des Leitungsbandes          | eV            |

| $W_V$       | max. Energie des Valenzbandes            | eV            |

| $x_d$       | Weite der Raumladungszone                | m             |

#### Verwendete Abkürzungen

| Abkürzung | Bedeutung                                       |

|-----------|-------------------------------------------------|

| AA        | Active Area                                     |

| BL        | Bitleitung $(n^+ \text{ Gebiet})$               |

| CC        | Conventional Concept                            |

| CHE       | Channel Hot Electron                            |

| DIBL      | Drain Induced Barrier Lowering                  |

| INCE      | Inverse Narrow Channel Effect                   |

| LDD       | Lightly Doped Drain                             |

| LI        | Local Interconnect                              |

| LOCOS     | Local Oxidation of Silicon                      |

| LVZ       | Ladungsverlust nach Zykeln                      |

| MNOS      | Metal-Nitride-Oxide-Semiconductor               |

| NROM      | Nitride Read Only Memory                        |

| NVM       | Nonvolatile Memory                              |

| ONO       | Oxide-Nitride-Oxide                             |

| SONOS     | Semiconductor-Oxide-Nitride-Oxide-Semiconductor |

| STI       | Shallow Trench Isolation                        |

| WL        | Wortleitung (Gate)                              |

## Kapitel 1

## Einleitung

#### 1.1 Motivation für NROM

In den letzten fünf Jahren hat sich der Markt für nichtflüchtige Speicher rasant entwickelt. Er expandiert seit Jahren mit zweistelligen Zuwachsraten. Zudem gehen Analysten davon aus, dass in Zukunft der Anteil der nichtflüchtigen Speicher am gesamten Speichermarkt stetig wachsen wird. Gartner Dataquest rechnet bis 2007 mit einem Wachstum von durchschnittlich 20% pro Jahr, [11]. Dies ist in Abbildung 1.1 veranschaulicht.

Vor diesem Hintergrund ist der technische Fortschritt bei nichtflüchtigen Speichern von großer kommerzieller Bedeutung. Bisher ist das Floating Gate Konzept die häufigst verwendete Technologie für diese Klasse von Speichern. Durch die Attraktivität des Marktes und durch die stetig wachsenden Anforderungen drängen neuartige Konzepte in Richtung Realisierung und in Richtung Markt.

Eines dieser neuen Konzepte ist NROM. Es handelt sich hierbei um eine Technologie, die auf der lokalisierten Ladungsspeicherung in Nitrid basiert. Hierdurch wird es im Gegensatz zur herkömmlichen Floating Gate Technologie möglich, zwei physikalisch voneinander getrennte Bits in einer Zelle zu speichern. Zudem baut NROM auf einem normalen CMOS Prozess auf und somit aus prozesstechnischer Sicht auf weitgehend bekannten und produktionstauglichen Verfahren.

Abbildung 1.1: Wachstumsraten für verschiedene Segmente des Speichermarktes, [11].

Es gibt bereits erste Produkte mit dieser neuen Technologie auf dem Markt.

#### 1.2 Aufbau der Arbeit

Ziel dieser Arbeit ist es, einen Beitrag für das Verständnis, sowie für die Weiterentwicklung von NROM-Speicherzellen zu leisten. So wird neben den Modellbetrachtungen und der Vorstellung eines neuen Multilevel-Betriebs für NROM auch ein neuartiges Zellkonzept, das mit shallow trench isolation (STI) arbeitet, experimentell untersucht.

Für das Verständnis der Funktionsweise von NROM-Zellen ist es zuvor unerlässlich, das Verhalten der MOS-Struktur und des MOS-Transistors zu verstehen. Aus diesem Grund werden in Kapitel 2 die wesentlichen Grundlagen hierfür besprochen. Besonderes Augenmerk wird auf die Auswirkung von sub- $\mu m$  Effekten gelegt, da diese von großer Bedeutung für die hier behandelten Zellen sind. Zudem wird eine Einführung in die Funktionsweise von NROM-Speicherzellen gegeben.

In Kapitel 3 werden ein bekanntes Konzept und das neuartige STI-Konzept für NROM detailliert vorgestellt und besprochen. Zudem werden Modelle für wesentliche Aspekte der NROM-Zelle erörtert. Kapitel 4 beschäftigt sich mit der experimentellen Untersuchung des STI-Konzepts. Es werden eine Vielzahl von Messungen vorgestellt und deren Ergebnisse besprochen. Es wird gezeigt, dass die shallow trench isolated NROM-Zelle funktionstauglich ist. Zudem werden einige für dieses Konzept charakteristische Eigenschaften herausgearbeitet. Das Kapitel 5 stellt einen neuen Multilevel-Betrieb für NROM vor. Dieser macht NROM nicht nur multilevel tauglich, sondern verbessert auch für zwei Bits pro Zelle die Informationshaltung. Abschließend wird eine Zusammenfassung in Kapitel 6 gegeben.

## Kapitel 2

## Grundlagen

#### 2.1 MOS-Struktur

Die MIS-Struktur (Metall-Isolator-Halbleiter) bildet die Grundlage für den MOS-Feldeffekttransistor (hier ist der Isolator das natürliche Oxid des Siliziums,  $SiO_2$ , damit wird

aus MIS  $\rightarrow$  MOS) und damit auch für die NROM-Speicherzelle. Aus diesem Grund wird

hier auf die grundlegende Funktionsweise der MOS-Stuktur eingegangen.

Abbildung 2.1 zeigt die Verhältnisse einer MOS-Struktur, wenn zwischen Gate und Bulk ( $\equiv$  Substrat) eine Spannung  $U_{GB} > 0V$  angelegt wird. Der Halbleiter ist homogen p-dotiert mit der Dichte  $N_A$ . Das positive Potential des Metalls gegenüber dem Halbleiter führt zu einer negativen Influenzladung an der Halbleiteroberfläche, welche durch eine entsprechende positive Oberflächenladung auf der Metalloberfläche kompensiert wird. Da die Raumladungsdichte stückweise konstant ist, folgt aus

$$div\vec{E} = -\frac{\rho}{\epsilon_0 \epsilon_r},\tag{2.1}$$

dass die resultierende elektrische Feldstärke linear verläuft. Im Oxid, das als Isolator raumladungsfrei ist, ist die Feldstärke konstant, siehe Bild 2.1 b.

Ausgangspunkt für die Berechnung des Feldverlaufs ist die Poissongleichung:

$$\frac{d^2\phi}{dx^2} = -\frac{\rho(x)}{\epsilon_0 \epsilon_{Si}} \tag{2.2}$$

Abbildung 2.1: MOS-Struktur; a) Ladungsträgerverteilung; b) Feldverteilung bei charge-sheet Näherung; c) resultierender Spannungsverlauf; [24].

wobei für die Raumladungsdichte  $\rho$  unter Annahme vollständiger Ionisation gilt:

$$\rho(x) = -q[N_A + n(x) - p(x)] \tag{2.3}$$

Mit der Schottky-Näherung, d.h. mit völliger Verdrängung der beweglichen Ladungsträger aus der Raumladungszone im Halbleiter (p(x) = 0), ergibt sich für die Feldstärkenberechnung:

$$\int_{E(x)}^{E(x_d)} dE(x) = -\frac{q}{\epsilon_0 \epsilon_{Si}} \int_x^{x_d} (N_A + n(x)) dx \qquad \text{für} \qquad 0 \le x \le x_d$$

(2.4)

Zum Lösen dieser Gleichung ist eine zusätzliche Näherung hilfreich. Die Ausdehnung der Raumladungszone,  $x_d$ , ist groß im Vergleich mit der Debye-Länge,  $L_{Dp}$ . Weiterhin lässt

sich zeigen, dass die Dicke der Inversionsschicht,  $d_i$ , klein ist gegenüber der Debye-Länge, [33]. Es gilt also:  $d_i \ll L_{Dp} \ll x_d$ . Daher kann mit guter Näherung angenommen werden, dass das gesamte Potential  $\phi_S$  über der Verarmungszone abfällt. Diese Annahme wird als Charge Sheet Näherung bezeichnet, [24]. Mit ihrer Hilfe folgt aus Gleichung (2.4):

$$E_{Si}(x) = \frac{qN_A}{\epsilon_0 \epsilon_{Si}} (x_d - x) \tag{2.5}$$

und mit  $E = -grad(\phi)$  für die Spannung:

$$\phi(x) = \frac{qN_A}{2\epsilon_0\epsilon_{Si}}(x_d - x)^2 \tag{2.6}$$

Damit lässt sich die Oberflächenspannung,  $\phi_S$ , leicht berechnen zu:

$$\phi(x=0) = \phi_S = \frac{qN_A}{2\epsilon_0 \epsilon_{Si}} x_d^2 \tag{2.7}$$

Unter Berücksichtigung der Schottky-Näherung lässt sich nun die flächenbezogene Ladung der Raumladungszone berechnen:

$$\sigma_d = -qN_A x_d = -\sqrt{2qN_A \epsilon_0 \epsilon_{Si} \phi_S} \tag{2.8}$$

Die zweite Ladung, die sich unter dem Oxid befindet, ist die Ladung des Inversionskanals  $\sigma_n$ . Sie ist von entscheidender Bedeutung für die Funktion des Transistors. Mit Hilfe des Gaußschen Satzes, [52],

$$Q = \oint \vec{D} \cdot d\vec{A} \tag{2.9}$$

gelangen wir zu:

$$\sigma_n + \sigma_d = -D_{ox} \tag{2.10}$$

Zudem gilt:

$$D_{ox} = \epsilon_0 \epsilon_{ox} \frac{d\phi}{dx}$$

$$= \epsilon_0 \epsilon_{ox} \frac{\phi_{ox}}{d_{ox}}$$

$$= C'_{ox} \phi_{ox}$$

(2.11)

2.1. MOS-STRUKTUR 7

hierbei ist  $C'_{ox}$  die flächenbezogene Oxidkapazität und  $\phi_{ox}$  die über der Oxidschicht abfallende Spannung.

Für die weiteren Berechnungen wird an dieser Stelle die Flachbandspannung,  $U_{FB}$ , eingeführt. Das ist diejenige Spannung, die man von außen an eine Halbleiterstruktur anlegen muss, damit die Bänder im Bändermodell des Halbleiters waagerecht verlaufen.  $U_{FB}$  ist somit die Summe der Kontaktspannungen zwischen Metall und Halbleiter,  $\phi_K$ , und zwischen verschieden dotierten Bereichen im Halbleiter,  $\phi_i$ . Für die Flachbandspannung gilt:

$$U_{FB} = \phi_K + \phi_i$$

$$= \phi_K + \phi_t \cdot \ln \frac{N_{A2}}{N_{A1}}$$

(2.12)

$N_{A1}$  und  $N_{A2}$  sind zwei unterschiedlich dotierte Gebiete im Silizium.  $\phi_t$  ist die Temperaturspannung:

$$\phi_t = \frac{kT}{q} \tag{2.13}$$

Nach der Einführung der Flachbandspannung, wird wieder Abbildung 2.1 betrachtet, speziell Teil c). Aus diesem lässt sich leicht ablesen, dass gilt:

$$U_{GB} = \phi_{ox} + \phi_S + U_{FB} \tag{2.14}$$

Löst man diese Gleichung nach  $\phi_{ox}$  auf und setzt dies in Gleichung (2.11) ein, so ergibt sich:

$$D_{ox} = C'_{ox} \left( U_{GB} - \phi_S - U_{FB} \right) \tag{2.15}$$

Nun kann die Ladung der Inversionsschicht unter Verwendung der Beziehungen (2.8) und (2.10) berechnet werden zu:

$$\sigma_n = -C'_{ox} \left( U_{GB} - U_{FB} - \phi_S \right) + \sqrt{2qN_A \epsilon_0 \epsilon_{Si} \phi_S}$$

$$= -C'_{ox} \left( U_{GB} - U_{FB} - \phi_S - \gamma \sqrt{\phi_S} \right)$$

(2.16)

Um die Übersichtlichkeit der Gleichung zu verbessern, ist der Faktor  $\gamma$  eingeführt worden. Er wird als Substratsteuerfaktor bezeichnet und ist definiert als:

$$\gamma = \frac{1}{C_{ox}'} \sqrt{2q N_A \epsilon_0 \epsilon_{Si}} \tag{2.17}$$

Dieser Faktor wird im weiteren Verlauf der Arbeit noch häufiger betrachtet werden, da er dazu dient, die Eigenschaften von Transistoren bzw. NROM-Speicherzellen zu beschreiben.

Abbildung 2.2: Betrag der Inversionsschichtladung pro Fläche, aufgetragen über der Gate-Substrat-Spannung.

In Abbildung 2.2 lässt sich erkennen, dass man durch Extrapolation der Kurve in starker Inversion auf  $\sigma_n = 0$  die Spannung  $U_{th}$  erhält. Diese Spannung wird als Einsatzspannung bezeichnet. Für die Berechnung erkennt man dann aus Abbildung 2.3, dass in starker Inversion große Änderungen von  $U_{GB}$  nur sehr kleine Änderungen von  $\phi_S$  zur Folge haben. Daher ist die Näherung üblich, dass in starker Inversion die Oberflächenspannung als konstant betrachtet wird, [69]:

$$\phi_S \approx \phi_0 \tag{2.18}$$

Dies ergibt zusammen mit Gleichung (2.16) für  $\sigma_n = 0$  die Einsatzspannung:

$$U_{th} = U_{FB} + \phi_0 + \gamma \sqrt{\phi_0} \tag{2.19}$$

An dieser Stelle wird darauf hingewiesen, dass die Einsatzspannung eine Größe ist, die mit Hilfe einer Gleichung berechnet wird, welche für starke Inversion gilt. Die MOS-Struktur ist bei der Spannung  $U_{GB} = U_{th}$  jedoch noch nicht in starker Inversion, was an Bild 2.2 verdeutlicht wird.

Abbildung 2.3: Oberflächenspannung über Gate-Substrat-Spannung (rechts) und Ladungen über Oberflächenspannung (links)

Um die Anwendbarkeit von Gleichung (2.19) zu erleichtern, wird eine Näherung für den Wert  $\phi_0$  bei starker Inversion benötigt. Hierzu dient Abbildung 2.3, die in ähnlicher Form z.B. bei Tsividis, [69], zu finden ist. Der Wert  $\phi_0$  ist schwer exakt zu bestimmen, er ist in der Abbildung 2.3 jedoch annähernd  $2\phi_F + \phi_{Z0}$ . Hierbei ist  $\phi_F$  die Fermispannung, die durch

$$\phi_F = \phi_t \cdot \ln \frac{N_A}{n_i} \tag{2.20}$$

gegeben ist.

Am häufigsten wird in starker Inversion  $\phi_0$  genähert mit:

$$\phi_0 = 2\phi_F$$

siehe z.B.: [24],[69] (2.21)

Unter Betrachtung von Abbildung 2.3 ist diese Näherung jedoch nicht sonderlich exakt. Man sieht, dass die Oberflächenspannung noch weiter ansteigt, wenn  $U_{GB}$  erhöht wird.

Genauer wäre:

$$\phi_0 = 2\phi_F + \Delta\phi \tag{2.22}$$

Die Angabe von  $\Delta \phi$  ist allerdings schwierig. Für ein homogen dotiertes Substrat beträgt sie einige  $\phi_t$ , ( $\Delta \phi \approx 6\phi_t$ ). Für nicht homogen dotierte Substrate, wie sie in der Realität meist auftreten, kann  $\Delta \phi$  jedoch deutlich von diesem Wert abweichen.

#### 2.2 MOS-Transistor

Der MOS-Transistor beruht wesentlich auf der in Abschnitt 2.1 besprochenen Zweipol-MOS-Struktur. Eine schematische Darstellung eines MOS-Transistors ist in Abbildung 2.4 mit dem zugehörigen Ausgangskennlinienfeld abgebildet.

Abbildung 2.4: Schematische Darstellung eines Transistors (links) und dessen Ausgangskennlinienfeldes (rechts)

Im hier behandelten Fall eines n-Kanal Transistors (p-dotiertes Substrat) sind gegenüber

der Zweipol-MOS-Struktur zwei hochdotierte n-Gebiete, Source und Drain, hinzugekommen. Die allgemeine Funktionsweise eines Transistors soll hier nicht Erklärungsgegenstand sein, vielmehr soll auf Aspekte eingegangen werden, die für die untersuchten sub  $\mu m$  - Speicherzellen von großer Bedeutung sind. Grundlegendes zum Transistor ist leicht in der Literatur zu finden, z.B. [24],[29],[33],[69],...

Eine elementare Größe ist die Einsatzspannung,  $U_{th}$ , des Transistors, insbesondere da ihre Verschiebung als Mittel zur Informationsspeicherung in NROM-Zellen verwendet wird. Hier muss eine Anpassung der Gleichung (2.19) aus Abschnitt 2.1 erfolgen. Für die Einsatzspannung eines Transistors ist die Gate-Source-Spannung,  $U_{GS}$ , wichtig, die nicht zwangsweise mit der Gate-Substrate-Spannung,  $U_{GB}$ , identisch ist. Daher gilt Gleichung (2.19) nur für einen Transistor, wenn die Source-Substrat-Spannung gleich Null ist ( $U_{SB} = 0$ ). Sonst muss Gleichung (2.16) angepasst werden, woraus sich für die Einsatzspannung des Transistors ergibt:

$$U_{th} = U_{FB} + \phi_0 + \gamma \sqrt{\phi_0 + U_{SB}} \tag{2.23}$$

Für  $\phi_0$  gelten weiterhin die Gleichungen aus Abschnitt 2.1.

Darüber hinaus ist es für das Verständnis des Programmierens einer NROM-Zelle von Bedeutung, den Operationsbereich auf dem Kennlinienfeld zu kennen. Wie später näher erläutert wird, werden NROM-Zellen mit heißen Elektronen programmiert; ob und wo diese auftreten, hängt von den Betriebsbedingungen der Zelle ab. Aus diesem Grund soll hier der Übergang vom Widerstandsbereich in den Sättigungsbereich näher betrachtet werden. Dies ist im Ausgangskennlinienfeld in Abbildung 2.4 veranschaulicht. Die gestrichelte Linie stellt den Übergang zwischen den beiden Bereichen dar. Die Drain-Source-Spannung, bei der dieser Übergang stattfindet, wird Drain-Source-Sättigungsspannung,  $U'_{DS}$ , genannt. Sie lässt sich errechnen aus:

$$U'_{DS} = \frac{U_{GS} - U_{th}}{\alpha} \tag{2.24}$$

$\alpha$ ist ein Anpassungsfaktor, der nachfolgend näher betrachtet wird. Zur Spannung  $U_{DS}^{\prime}$

gehört ein Drain-Sättigungsstrom bei  $(U_{DS}=U_{DS}^{\prime})$  von:

$$I'_{DS} = \frac{W}{L} \mu C'_{ox} \frac{(U_{GS} - U_{th})^2}{2\alpha}$$

(2.25)

wobei W die Weite des Transistors und L seine Länge ist.  $\mu$  ist die Beweglichkeit der Ladungsträger im Kanal. Für den Strom zwischen Drain und Source gilt insgesamt, [69]:

$$I_{DS} = \begin{cases} \frac{W}{L} \mu C'_{ox} \left[ (U_{GS} - U_{th}) U_{DS} - \frac{\alpha}{2} U_{DS}^2 \right], & U_{DS} \leq U'_{DS} \\ \frac{W}{L} \mu C'_{ox} \frac{(U_{GS} - U_{th})^2}{2\alpha} & U_{DS} > U'_{DS} \end{cases}$$

(2.26)

Es steht noch die Wahl für den Wert von  $\alpha$  aus. In älteren oder einfachen Transistormodellen findet man häufig für  $\alpha$ :

$$\alpha_0 = 1 \tag{2.27}$$

Diese Näherung bedeutet, dass die Tiefe der Verarmungsschicht über den ganzen Kanal als konstant angenommen wird. Die Tiefe wird überall gleich der Tiefe an der Source-Seite gesetzt. Dies hat eine Unterschätzung von  $|\sigma_d|$  und eine Überschätzung von  $|\sigma_n|$  zur Folge. Aus dieser Tatsache resultiert ein zu großer Wert für  $I_{DS}$ . Dieser Fehler wird besonders groß, wenn  $\gamma$  nicht klein ist. Zudem bekommt man für  $U'_{DS}$  zu hohe Werte.

In anderen Transistormodellen wird ein Wert angegeben, der aus einer Taylor-Reihenentwicklung abgeleitet wird, [50]:

$$\alpha_1 = 1 + \frac{\gamma}{2\sqrt{\phi_0 + U_{SB}}} \tag{2.28}$$

Diese Gleichung liefert nur für kleine Werte von  $U_{DS} = U_{DB} - U_{SB}$  gute Werte. Im Allgemeinen wird  $|\sigma_d|$  überschätzt und  $|\sigma_n|$  unterschätzt. Dies resultiert in zu niedrigen Werten für  $I_{DS}$  und  $U'_{DS}$ . Die Fehler gehen also in die entgegengesetzte Richtung im Vergleich mit Gleichung (2.27). Es liegt daher nahe, in Gleichung (2.28) einen Korrekturfaktor einzuführen, damit folgt:

$$\alpha_2 = 1 + d_1 \frac{\gamma}{2\sqrt{\phi_0 + U_{SB}}} \tag{2.29}$$

Für diesen Korrekturfaktor,  $d_1$ , werden in der Literatur Werte zwischen 0,5 und 0,8 verwendet,[34],[50].

#### 2.3 MOS-Transistor im sub $\mu m$ - Bereich

In diesem Abschnitt werden Effekte behandelt, die bei besonders kleinen Bauelementen auftreten. Die Speicherzellen, die in dieser Arbeit behandelt werden, haben elektrische Dimensionen von Länge zu Weite in der Größenordnung von 150nm zu 100nm, und sind somit tief im sub-Mikrometer-Bereich. Die hier beschriebenen Mechanismen sollen in erster Linie dem besseren Verständnis dienen und weniger, um Formeln zur realitätsnahen Berechnung zu liefern.

#### 2.3.1 Kanallängenmodulation

Die Kanallängenmodulation kann als Kurzkanaleffekt betrachtet werden. Da sie jedoch auch bei z.B.  $10\mu m$  langen Transistoren beobachtet werden kann, wird sie hier nicht unter Kurzkanaleffekten behandelt. Die Kanallängenmodulation ist für spätere Betrachtungen wichtig.

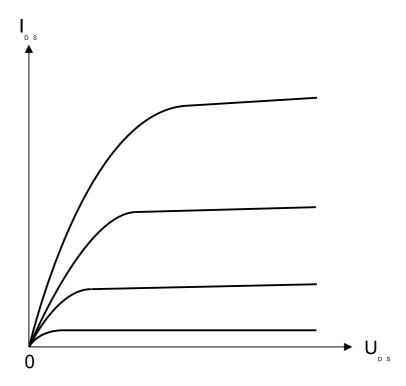

Abbildung 2.5: Kennlinienfeld unter Einfluss von Kanallängenmodulation

In Abbildung 2.5 ist die Auswirkung der Kanallängenmodulation zu sehen. Im Gegensatz, zu dem in Abbildung 2.4 dargestellten Kennlinienfeld, verlaufen die Kurven im Sättigungsbereich nicht mehr horizontal. Der Drain-Source-Strom steigt auch in diesem Bereich bei Erhöhung von  $U_{DS}$  weiter leicht an.

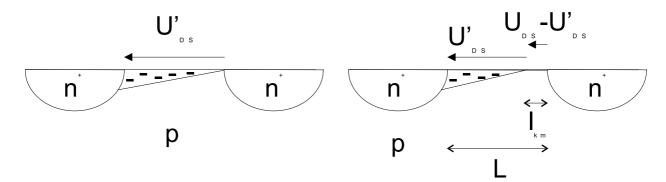

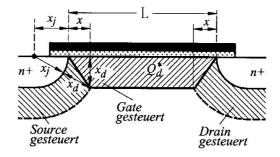

Abbildung 2.6 bietet eine anschauliche Erklärung für die Kanallängenmodulation. Dies hat nicht den Anspruch, eine exakte Beschreibung zu sein. So wird in dieser Betrachtung das am Gate anliegende Potential nicht für den Feldverlauf nahe der Drain berücksichtigt.

Abbildung 2.6: links: Transistor am pinchoff; rechts: Transistor bei weiter erhöhter Drain-Source-Spannung

Auf der linken Seite der Abbildung ist der Transistor am pinchoff-Punkt ( $U_{DS} = U'_{DS}$ , vgl. Abbildung 2.4). Für diese Betrachtung nehmen wir an, dass pinchoff auftritt, wenn betragsmäßig die Inversionsschichtladung  $|\sigma_n|$  an der Drain sehr klein ist. Dies bedeutet eine sehr viel kleinere Ladung als die der Verarmungszone  $|\sigma_d|$ . Wenn die Spannung  $U_{DS}$  weiter über  $U'_{DS}$  hinaus erhöht wird, so nimmt die Ladung der Inversionsschicht am Drain-Ende weiter ab. Der pinchoff-Punkt verschiebt sich weiter nach links, wie es auf der rechten Seite der Abbildung 2.6 dargestellt ist. Dies bedeutet jedoch nicht, dass kein Strom mehr zwischen Source und Drain fließt, was zudem der Kontinuitätsgleichung widersprechen würde. Wie allgemein von pn-Übergängen bei Bipolar-Transistoren bekannt ist, können große Ströme durch Verarmungszonen fließen. Die Elektronen müssen sich in diesem Bereich mit sehr hoher Geschwindigkeit bewegen, damit bei sehr kleinen Werten von  $|\sigma_n|$  ein großer Strom zustande kommt.

Die Bedingung, dass die Elektronen sich zwischen dem pinchoff-Punkt und der Drain mit sehr hoher Geschwindigkeit bewegen, wird als eine weitere Definition für den pinchoff verwendet. Sie besagt, dass der pinchoff-Punkt derjenige Punkt ist, ab dem die Elektronen sich mit Sättigungsgeschwindigkeit bewegen.

In Abbildung 2.6 ist rechts gezeigt, dass über dem Kanal von der Source bis zum pinchoff-Punkt stets die Spannung  $U'_{DS}$  abfällt, der Rest der Spannung  $U_{DS}-U'_{DS}$  fällt zwischen dem pinchoff-Punkt und der Drain ab. Diese Strecke wird mit  $l_{km}$  bezeichnet. Es ist leicht nachvollziehbar, dass die Strecke  $l_{km}$  immer größer wird, je mehr  $U_{DS}$  die Sättigungsspannung  $U'_{DS}$  überschreitet. Dies ist gleichbedeutend mit einer Verkürzung der Inversionsschicht. Dieser Vorgang wird als Kanallängenmodulation bezeichnet.

Mit der Annahme, dass das Feld in der Verarmungszone horizontal verläuft, kann mit Hilfe der Poisson-Gleichung ein Wert für  $l_{km}$  angegeben werden, [69]:

$$l_{km} = \sqrt{\frac{2\epsilon_0 \epsilon_{Si}}{qN_A}} \left[ \sqrt{\phi_D + (U_{DS} - U'_{DS})} - \sqrt{\phi_D} \right]$$

(2.30)

wobei für  $\phi_D$  gilt:

$$\phi_D = \frac{\epsilon_0 \epsilon_{Si} E_k^2}{2q N_A} \tag{2.31}$$

$E_k$  ist die kritische Feldstärke oberhalb derer sich die Elektronen mit Sättigungsgeschwindigkeit bewegen.  $E_k$  liegt hier in horizontaler Richtung an. Bei der Betrachtung von Elektronen sind für  $E_k$  Werte im Bereich  $8 \times 10^3 \dots 3 \times 10^4 V/cm$  einzusetzen. Dies ergibt sich durch

$$E_k = \frac{|v_{e,max}|}{\mu} \tag{2.32}$$

und beruht auf folgenden Annahmen:

maximale Elektronengeschwindigkeit:

$$|v_{e,max}| = 5 \times 10^6 \dots 2 \times 10^7 \frac{cm}{s}$$

(2.33)

Elektronenbeweglichkeit:

$$\mu = 650 \frac{cm^2}{Vs}$$

(2.34)

Ein zur Gleichung (2.30) sehr ähnlicher Ausdruck wurde von Reddi und Sah vorgestellt,

[56]:

$$l_{km,2} = \sqrt{\frac{2\epsilon_0 \epsilon_{Si}}{q N_A} \left( U_{DS} - U_{DS}' \right)} \tag{2.35}$$

Verglichen mit Gleichung (2.30) liefert (2.35) größere Werte. Sie ist für Zellen mit einer Kanallänge von  $2...4\mu m$  und Dotierungen im Bereich  $N_A = 10^{15}...10^{16}cm^{-3}$  geeignet, [75], [16]. Für Zellen mit einer Kanallänge von nur  $\sim 200nm$  wird die Strecke zwischen pinchoff-Punkt und Drain mit der Gleichung (2.35) überschätzt. Die gleiche Tendenz gilt für Gleichung (2.30), dennoch sind beide Gleichungen für das Verständnis hilfreich.

Nun lässt sich der Anstieg des Source-Drain-Stromes im Sättigungsbereich der Kennlinien aus Abbildung 2.5 erklären. Der Sättigungsstrom ist aus Gleichung (2.25) bekannt:

$$I'_{DS} = \frac{W}{L} \mu C'_{ox} \frac{(U_{GS} - U_{th})^2}{2\alpha}$$

$$= c_1 \frac{1}{L}$$

(2.36)

Für Spannungen die größer als  $U'_{DS}$  sind, muss Gleichung (2.26) modifiziert werden zu:

$$I_{DS} = c_1 \frac{1}{L - l_{km}} \tag{2.37}$$

Aus den Gleichungen (2.36) und (2.37) ergibt sich:

$$I_{DS} = \frac{I'_{DS}}{1 - \frac{l_{km}}{L}} \tag{2.38}$$

Aus dieser Gleichung lässt sich unmittelbar ablesen, dass ein weiteres Erhöhen von  $U_{DS}$  oberhalb von  $U'_{DS}$ , welches eine Vergrößerung von  $l_{km}$  hervorruft, in einem Anstieg des Source-Drain-Stromes,  $I_{DS}$ , resultiert.

Ein vereinfachtes empirisches Modell wurde von Merckel, [48], vorgeschlagen. Der Source-Drain-Strom berechnet sich hierzu:

$$I_{DS} = I'_{DS} \left( 1 + \frac{U_{DS} - U'_{DS}}{U_A + U'_{DS}} \right) \tag{2.39}$$

$U_A$  wird als Early-Spannung bezeichnet, für sie gilt:

$$U_A = k_A L \sqrt{N_A} \tag{2.40}$$

wobei  $k_A$  ein Proportionalitätsfaktor ist, der im Bereich  $1 \times 10^{-3} \dots 2 \times 10^{-3} V \cdot cm^{1/2}$  liegt. Die Spannung  $U_A$  erhält man, indem man die Kennlinie im Sättigungsbereich nimmt und diese bis  $I_{DS} = 0$  extrapoliert.

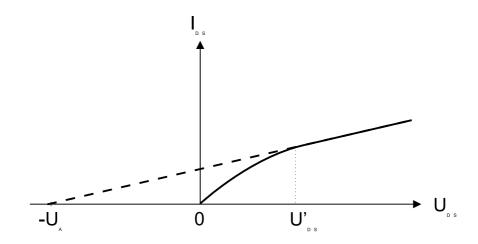

Abbildung 2.7: Vereinfachtes Modell zur Kanallängenmodulation

Dies ist in Abbildung 2.7 dargestellt. Die extrapolierten Kurven für verschiedene Werte von  $U_{GS}$  schneiden die x-Achse in einem Punkt, nämlich bei  $-U_A$ .

#### 2.3.2 Ladungsträgerbeweglichkeit

Die Beweglichkeit der Elektronen im Kanal nimmt bei kleinen Dimensionen ab. Hierzu ist von K. Chen et al.,[8], [9], ein Modell für die Ladungsträgerbeweglichkeit vorgeschlagen worden. Die Abhängigkeit der Beweglichkeit von der effektiven Feldstärke ist in Abbildung 2.8 (es gilt:  $T_{ox} = d_{ox}$ ) dargestellt.

Da für NROM-Speicherzellen immer n-Kanal Transistoren verwendet werden, ist hier in erster Linie die Beweglichkeit der Elektronen von Interesse. Für sie gilt im Rahmen der Achsenbeschriftung  $\alpha=0$ .

Die Abhängigkeit der Beweglichkeit kann als Funktion der effektiven, vertikalen elektrischen Feldstärke in der Inversionsschicht ausgedrückt werden, [58]. Diese berechnet sich

Abbildung 2.8: Modell für die Ladungsträgerbeweglickeit von NMOS Elektronen und PMOS Löchern zusammen mit experimentellen Daten,[8]

für Elektronen zu:

$$E_{eff} = C'_{ox} \frac{\frac{U_{GS} - U_{th}}{2} + U_{th}}{\epsilon_0 \epsilon_{Si}} = \frac{\epsilon_0 \epsilon_{ox}}{d_{ox}} \frac{U_{GS} + U_{th}}{2\epsilon_0 \epsilon_{Si}}$$

$$= \frac{U_{GS} + U_{th}}{6d_{ox}}$$

(2.41)

Unter Verwendung dieser Gleichung lässt sich eine Beziehung für die Beweglichkeit der Elektronen angeben, die in ähnlicher Form auch von Liang et al.,[38], vorgeschlagen wurde:

$$\mu_n(U_{GS}, U_{th}, d_{ox}) = \frac{540}{1 + \left(\frac{E_{eff}}{0.9}\right)^{1.85}}$$

$$= \frac{540}{1 + \left(\frac{U_{GS} + U_{th}}{5.4d_{ox}}\right)^{1.85}}$$

(2.42)

Es gelten folgende Dimensionen für diese Formel:  $\mu_n$  in  $cm^2/(Vs)$ ,  $E_{eff}$  in MV/cm,  $U_{GS}$  und  $U_{th}$  in MV und  $d_{ox}$  in cm.

Bei Anwendung der Gleichung (2.42) für eine Einsatzspannung von  $U_{th} = 2V$  und eine Oxiddicke von  $d_{ox} = 20nm$  ergibt sich der in Abbildung 2.9 dargestellte Verlauf der Elektronenbeweglichkeit als Funktion der Gate-Source-Spannung.

Abbildung 2.9: Elektronenbeweglichkeit als Funktion von  $U_{GS}$  für  $U_{th}=2V$  und  $d_{ox}=20nm$

### 2.3.3 Kurzkanaleffekt

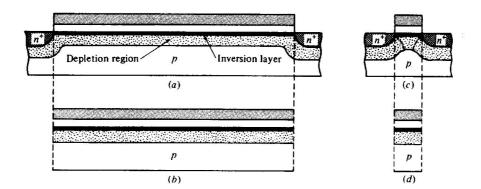

Bei der Herleitung der Einsatzspannung  $U_{th}$  (vgl. Gleichungen (2.19) und (2.23)) sind die Auswirkungen der Source- und Drain-Gebiete nicht berücksichtigt worden. Es wurde dasjenige Potential ermittelt, welches benötigt wird, um einen Inversionskanal in einer MOS-Struktur zu erzeugen. Die Situation ist in Abbildung 2.10 dargestellt.

Die Vernachlässigung der Randbereiche ist für Transistoren mit einer großen Kanallänge eine gute Näherung, wie der Vergleich von (a) und (b) verdeutlicht. Wird die Kanallänge jedoch sehr klein, so haben die Raumladungszonen der Source- bzw. Drain-Gebiete eine nicht mehr zu vernachlässigbare Auswirkung. Man sieht, dass Ausschnitt (d) keine gute Näherung für die Situation in Ausschnitt (c) ist. Der Transistor (c) hat eine geringere Einsatzspannung und damit bei gleicher Drain-Source-Spannung einen höheren Strom  $I_{DS}$ , als man dies aus einer Betrachtung von (d) ableiten würde.

Die Tatsache, dass die Verarmungszone unter dem Gate nicht mehr nur durch das Gatepotential gesteuert wird, sondern auch durch die Raumladungszonen der pn-Übergänge von

Abbildung 2.10: (a) Langkanal Transistor; (b) Kanal von (a) unter Vernachlässigung der Randeffekte; (c) Kurzkanal Transistor; (d) Kanal von (c) unter Vernachlässigung der Randeffekte; [69].

Source und Drain beeinflusst wird, wird als charge-charring bezeichnet. Ein einfaches Trapezmodell aus der Literatur, [71], [76], ist in Abbildung 2.11 dargestellt.

Abbildung 2.11: Trapezmodell zur Beschreibung des charge-charring bei  $U_{DS}=0V,[24].$

Die Einsatzspannung ist aus Gleichung (2.23) als

$$U_{th} = U_{FB} + \phi_0 + \gamma \sqrt{\phi_0 + U_{SB}}$$

$$= U_{FB} + \phi_0 - \frac{Q_d}{C_{ox}}$$

(2.43)

bekannt. Mit

$$Q_d = \sigma_d \cdot W \cdot L, \tag{2.44}$$

wird die Ladung der Verarmungszone bezeichnet, die durch das Gate verursacht wird. Das Trapezmodell besagt, dass nur noch die Ladung  $Q_d^*$  durch das Gate gesteuert wird. Für diese Ladung ist aus Abbildung 2.11 abzulesen:

$$Q_d^* = \sigma_d \cdot W \cdot (L - W) \tag{2.45}$$

Unter Verwendung von

$$(x_j + x)^2 + x_d^2 = (x_j + x_d)^2$$

(2.46)

lässt sich die Abhängigkeit der Einsatzspannung von der reduzierten Kanallänge L berechnen zu:

$$U_{th} = U_{FB} + \phi_0 + \frac{Q_d^* \cdot Q_d}{Q_d \cdot C_{ox}}$$

$$= U_{FB} + \phi_0 + \underbrace{\left[1 - \frac{x_j}{L} \left(\sqrt{1 + 2\frac{x_d}{x_j}} - 1\right)\right]}_{F_S} \gamma \sqrt{\phi_0 + U_{SB}}$$

$$= U_{FB} + \phi_0 + F_S \cdot \gamma \sqrt{\phi_0 + U_{SB}}$$

(2.47)

$F_S$  beschreibt die Absenkung der Einsatzspannung. Die Differenz gegenüber der in Gleichung (2.23) berechneten Einsatzspannung beträgt:

$$\Delta U_{th,cc1} = -\left(1 - \frac{Q_d^*}{Q_d}\right)\gamma\sqrt{\phi_0 + U_{SB}} \tag{2.48}$$

Gleichung (2.47) lässt sich weiter vereinfachen, indem man  $F_S$  in eine Taylor-Reihe entwickelt und die Glieder höherer Ordnung vernachlässigt,[49]. Zur Kompensation dieser Vernachlässigung wird ein Anpassungsfaktor  $\beta_1$  eingeführt, der normalerweise gleich eins gesetzt wird.

$$\frac{Q_d^*}{Q_d} = 1 - \beta_1 \frac{x_d}{L} \tag{2.49}$$

Verwendet man diese Gleichung, um die Differenz in der Einsatzspannung zu berechnen, so ergibt sich schließlich:

$$\Delta U_{th,cc2} = -2\beta_1 \frac{\epsilon_{Si} \cdot d_{ox}}{\epsilon_{ox} \cdot L} \left( \phi_0 + U_{SB} \right) \tag{2.50}$$

Man erkennt an Gleichung (2.50) leicht, dass eine kürzere Kanallänge durch ein dünneres Gateoxid kompensiert werden kann.

### Drain induced barrier lowering (DIBL)

Die bisherigen Betrachtungen im Abschnitt 2.3.3 wurden nur für vernachlässigbar kleine Drain-Source-Spannungen gemacht. Wird jedoch  $U_{DS}$  erhöht und somit auch die Drain-Bulk-Spannung  $U_{DB}$ , so vergrößert sich die Verarmungszone an der Drain. Die Einsatzspannung sinkt folglich mit steigender Spannung  $U_{DS}$  weiter ab.

Zur Berechnung kann ähnlich wie oben vorgegangen werden, jedoch wird das Trapez verzerrt. Es ergibt sich eine Anpassung von Gleichung (2.50) zu:

$$\Delta U_{th,cc2} = -2\beta_1 \frac{\epsilon_{Si} \cdot d_{ox}}{\epsilon_{ox} \cdot L} \left[ (\phi_0 + U_{SB}) + \beta_2 U_{DS} \right]$$

(2.51)

Aus der Rechnung folgt  $\beta_2 = 0, 25$ .  $\beta_2$  kann jedoch auch als Anpassungsfaktor verwendet werden.

Gleichung (2.51) wurde mit Hilfe des charge-sharing Modells errechnet. Es sagt aus, dass mit steigender Spannung  $U_{DS}$  die Einsatzspannung sinkt. Dies ist gleichbedeutend mit der Aussage, dass die Potentialbarriere für Elektronen zum Eintritt in den Kanal sinkt, [66]. Die Senkung der Barriere ist durch die Spannungsverhältnisse an der Drain verursacht, daher wird sie auch als Drain induced barrier lowering (DIBL) bezeichnet.

### 2.3.4 Schmalkanaleffekt

Bei schmalen Transistoren gewinnen die Randbereiche an Bedeutung. Die Auswirkung auf die Einsatzspannung hängt in diesem Fall wesentlich von den Art der seitlichen Begrenzung der Zellen ab. Hier werden zwei gebräuchliche Typen betrachtet, LOCOS (local oxidation of silicon) und STI (shallow-trench isolation). Sie sind anschaulich in Abbildung 2.12 dargestellt.

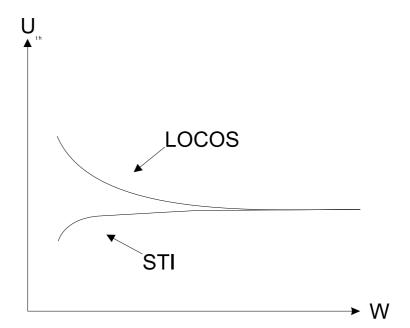

Die Auswirkungen auf die Einsatzspannungen von Transistoren, die auf diese beiden unterschiedlichen Weisen seitlich begrenzt werden, sind in Abbildung 2.13 zu sehen. Wie es zu diesem Verhalten kommt, wird im Folgenden besprochen.

Abbildung 2.12: Querschnitte durch Transistoren; oben: LOCOS isolierter Transistor; unten: shallow-trench-isolated (STI) Transistor; [69].

### **LOCOS** Isolation

Die Ausdehnung der Verarmungszone (bei positiver Gate-Spannung an einem NMOS-Transistor) ist bei dieser Art der Isolation seitlich nicht physikalisch begrenzt. Das Oxid wird zwar dicker zum Rand hin, aber es gibt einen Randbereich, der durch die Randfelder des Gates noch beeinflusst wird (siehe Abb. 2.12 oben). Im Randbereich werden ebenfalls die ionisierten Akzeptorladungen ausgeräumt. Somit wird durch das Gate ein Kanal gesteuert, der effektiv breiter ist, als die angenommene Breite. Bei sehr breiten Transistoren ist dieses Randvolumen der Verarmungszone verschwindend klein, bezogen auf das Gesamtvolumen der Verarmungszone und somit zu vernachlässigen. Ist ein Transistor jedoch

Abbildung 2.13: Effektiver Einsatzspannungsverlauf bei, bis auf die Isolation, identischen MOSFETs

sehr schmal, so erklärt dies, warum die Einsatzspannung steigt.

Dieser Effekt ist bei den NROM-Zellen, die in Kapitel 3.1 behandelt werden, zu beobachten. Sie sind von ihrer elektrischen Ausdehnung her seitlich nicht physikalisch begrenzt, bei ihnen hängt die elektrische Kanalweite maßgeblich von der anliegenden Gate-Spannung ab.

### **STI** Isolation

Im Gegensatz zur LOCOS Isolation kann sich der Kanal bei STI Isolation nicht über die Breite W des Transistors hin ausdehnen. In diesem Fall tragen die Randfelder des Gates sogar zu einer Verringerung der Einsatzspannung bei. Sie unterstützen das Ausräumen der Ladungsträger an den Außenkanten und erleichtern somit das Entstehen einer Inversionsschicht. Hierdurch sinkt die Einsatzspannung.

In der Praxis muss zusätzlich das Verhalten des Dotierstoffes im Kanalbereich berücksichtigt werden. Für eine p-Dotierung ist es üblich, Bor zu verwenden. Die Löslichkeit von Bor

in Oxid ist höher, als die in Silizium. Hierdurch kann es zu einer Segregation des Bors im Randbereich in das STI kommen. Dies hat eine lokal geringere Bor-Konzentration am Rand zur Folge. Es führt ebenfalls zu einer Senkung der Einsatzspannung.

Das Diffusions- und Segregationsverhalten ist z.B. von Jung et al.,[28], behandelt worden. Jung legt zudem die Auswirkung der Defekte, die durch die Source- bzw. Drain-Implantation entstehen, auf das Verhalten des Dotierstoffs an den verschiedenen Grenzflächen dar. So ist in der Mitte unter dem Gate ein Anreicherung von Bor zu beobachten, wohingegen es an der Kante zum STI zu einer Verarmung kommt.

Ist einer oder sind beide dieser Effekte stark ausgeprägt (kommt z.B. sogar eine physikalische Dünnung des Gateoxides hinzu), so kann es zu der Ausbildung eines 'corner-devices' führen. Dies bedeutet, dass am Rand ein Inversionskanal deutlich messbar zu einem früheren Zeitpunkt geöffnet wird als in der Mitte des Transistors. Man kann dies als eine Parallelschaltung von zwei 'Rand-Transistoren' und einem 'Mittel-Transistor' betrachten. Dies lässt sich bei starker Ausprägung durch einen 'hump' in der Kennlinie erkennen.

Das Absinken der Einsatzspannung bei kleinen Weiten (INCE=inverse narrow channel effect) ist jedoch nur bei STI-begrenzten Transistoren mit Oberflächenkanal zu beobachten, bei buried-channel Transistoren steigt, wie bei LOCOS Transistoren, die Einsatzspannung für kleine Weiten, [61], [36].

Die Auswirkungen des INCE können u.a. durch folgende Maßnahmen reduziert werden:

- Implantation in die Seitenwand, [37], [60]

- Abschrägung der Seitenwand, [61]

- Rundung der Kanten,[15]

Jedoch sind bei weiterer Verkleinerung der Strukturen nicht alle diese Möglichkeiten anwendbar, so bleibt z.B. kein Platz mehr für das Abschrägen der Seitenwände.

### 2.3.5 Heiße Elektronen

Heiße Elektronen (CHE = channel hot electrons) sind in normalen Transistoren unerwünscht, da sie zu Degradation und somit zu Alterung führen. Für NROM-Speicherzellen sind sie jedoch notwendig und folglich erwünscht.

Zuvor kommen wir aber zum Entstehungsprozess und zu den Eigenschaften von heißen Elektronen. Wie bereits diskutiert, steigt die horizontale Komponente der elektrischen Feldstärke von der Source zur Drain hin an. Der Wert ihres Maximums ist dabei sowohl von  $U_{DS}$ , wie auch von der Kanallänge, L, abhängig. Für kürzere Kanallängen steigt der Spitzenwert der Feldstärke für konstantes  $U_{DS}$  stark an. Überschreitet die horizontale Feldstärke den Wert der kritischen Feldstärke,  $E_k$ , (siehe Gl.(2.32)) so bewegen sich die Elektronen in guter Näherung ab diesem Punkt (pinchoff-Punkt) mit Sättigungsgeschwindigkeit bis zur Drain. Die Geschwindigkeit in Feldrichtung nimmt nicht mehr zu, jedoch steigt die kinetische Energie der Elektronen weiter. Diese wird jedoch durch zufällige Kollisionen immer wieder abgegeben. Einige der Elektronen in diesem Bereich gewinnen eine beträchtlich hohe Energie, sie werden als heiße Elektronen bezeichnet. Diese können durch Stoßionisation kovalente Bindungen aufschlagen und somit Elektronen-Loch-Paare erzeugen. Die erzeugten Elektronen werden durch das Feld zur Drain hin beschleunigt, wohingegen die Löcher zum Substrat hin abfließen. Durch den Fluß dieser Löcher kommt es zu einem Strom, der als Drain-Bulk Strom  $I_{DB}$ , bezeichnet wird.

Einige der erzeugten Elektronen besitzen so viel Energie, dass sie die Potentialbarriere des Gateoxides überwinden können und ins Gate abfließen. Da im Fall der NROM-Zelle das Gateoxid durch einen ONO-Stapel ersetzt wird, werden diese Elektronen dann mit einer hohen Wahrscheinlichkeit im Nitrid eingefangen. Dort verursachen sie dann die gewünschte Verschiebung der Einsatzspannung.

Die heißen Elektronen können jedoch auch, genauso wie bei üblichen Transistoren, negative Folgen haben. Ein kleiner Teil von ihnen schädigt die Silizium-Oxid-Grenzschicht und erhöht die Dichte der Grenzschichtzustände. Ein anderer Teil kann das Oxid selbst schädigen, indem er neue Störstellen erzeugt. Dies ist als Alterung bei herkömmlichen Transistoren, negative Folgen haben.

sistoren bekannt, [20],[26],[73]. Die Entstehung von heißen Elektronen kann stark reduziert werden, indem ein Teil der Drain nur schwach dotiert wird (LDD = Lightly Doped Drain), [54].

### Injektion von sekundären Elektronen

Für das Programmieren einer NROM-Zelle werden, wie erläutert, heiße Elektronen benötigt. Über die erwähnten negativen Folgen, die durch heiße Elektronen verursacht werden können, kommt für NROM noch eine weitere negative Auswirkung hinzu. Die Löcher, die bei der Stoßionisation entstehen, werden zum Substrat hin beschleunigt. Ein sehr geringer Anteil dieser Löcher sammelt so viel Energie auf diesem Weg, dass er seinerseits wieder Stoßionisationen durchführen kann. Dies geschieht deutlich tiefer im Silizium als das erste Aufbrechen von kovalenten Bindungen. Mit einer geringen Wahrscheinlichkeit können die bei dieser zweiten Stoßionisation entstandenen Elektronen (auch 'Sekundärelektronen' genannt) die Potentialbarriere des Oxides überwinden und werden im Nitrid des ONO (Oxid-Nitrid-Oxid Stapels) eingefangen. Somit verändern auch diese Sekundärelektronen die Einsatzspannung der Zelle.

Durch den tieferen Entstehungsort der Sekundärelektronen wird ein grosser Anteil von ihnen weiter zum Kanal hin injiziert, als die erwünschten Primaries. Somit wird die Verteilung der Elektronen breiter. Berücksichtigt man nun, dass die Injektionsposition der Löcher, die zum Löschen verwendet werden, nicht beliebig angepasst werden kann, so stellt sich heraus, dass Elektronen, die weit über dem Kanal (mit großem Abstand zum pn-Übergang) injiziert werden, später nicht mehr durch Löcher im gleichen Gebiet gelöscht werden können.

Um Sekundärelektronen beim späteren Löschen elektrisch zu kompensieren, müssen viele Löcher im Bereich des pn-Übergangs eingeschossen werden. Bei wiederholtem Programmieren und Löschen kann es so zu einer lokalen Anhäufung von Löchern kommen, die die Ladungsspeichereigenschaften der Zelle negativ beeinflusst.

Der Effekt der Sekundärelektronen hängt von einer ganzen Reihe von Parametern ab, so

z.B. der Wannendotierung, der Kanallänge und der Substratvorspannung. Auf diesen Effekt wird im weiteren Verlauf der Arbeit noch näher eingegangen.

### 2.3.6 Diodendurchbruch und Punchthrough

### Diodendurchbruch

Mit Diodendurchbruch ist hier der Durchbruch der Drain- bzw. Source-Substrat Diode gemeint. Wird z.B. an der Drain eine zu hohe Spannung gegenüber dem Substrat angelegt, so bricht die  $n^+p$ -Diode durch, und es fließt ein großer Strom direkt von der Drain ins Substrat. Dies begrenzt den Betriebsspannungsbereich der Speicherzelle. Der reine Diodendurchbruch ist von der Länge des Transistors unabhängig.

### Punchthrough

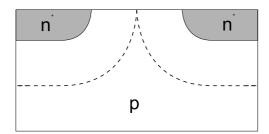

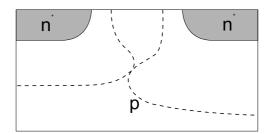

Der Punchthrough ist im Gegenteil zum Diodendurchbruch stark von der Kanallänge des Transistors abhängig. Punchtrough bezeichnet den Zustand, in dem sich die Raumladungszonen von Source und Drain berühren und so Ladungen direkt von Source zu Drain fließen können. Diese Betrachtungen werden ohne anliegende Gatespannung durchgeführt. Damit ist sofort klar, dass Punchthrough vor allem ein Problem kurzer Transistoren ist, [3],[25],[62].

Es werden zwei unterschiedliche Fälle von Punchthrough klassifiziert. Diese beiden Fälle sind in Abbildung 2.14 dargestellt.

Abbildung 2.14: Veranschaulichung der Verarmungszonen von Source und Drain; links: Oberflächen-Punchthrough; rechts: Punchtrough in der Tiefe

Links ist der Punchthrough an der Oberfläche dargestellt, rechts ist der Punchthrough in der Tiefe zu sehen. Welcher von beiden Fällen zuerst auftritt, hängt maßgeblich von dem Dotierprofil der Wanne ab. Aus der Erklärung mit Hilfe der Raumladungszonen, wie in Abbildung 2.14 zu sehen ist, wird unmittelbar eine Methode zum Verringern des Punchens nahegelegt. Die p-Dotierung der Wanne muss erhöht werden, um die Ausdehnung der Raumladungszonen zu verkleinern. Dann tritt der Punchthrough erst bei höheren Spannungen auf.

Bei den in dieser Arbeit behandelten NROM-Zellen mit Kanallängen in der Größenordnung von nur 100...200nm ist der Punchtrough ein kritischer Faktor. Beim Programmieren und Löschen wird mit hohen Spannungen an der Drain gearbeitet. Das Punchen kann vor allem die Löscheffizienz stark senken, oder ein Löschen sogar unmöglich machen, daher muss dieser Faktor stets beobachtet werden.

### 2.3.7 Subthreshold swing

Zur Beurteilung des Transistorverhaltens und seiner Güte wird häufig der subthreshold swing, S, verwendet. Er ist für den Bereich der schwachen Inversion definiert und gibt an, um wie viel die Spannung  $U_{GS}$  reduziert werden muss, damit der Drain-Strom,  $I_D$ , um eine Dekade gesenkt wird. Als Gleichung formuliert, bedeutet dies:

$$S = \frac{dU_{GS}}{d(\log I_{DS})} \tag{2.52}$$

Es ist klar, dass für einen guten Transistor kleine Werte für S gewünscht sind ( $\sim 80mV/Dekade$ ). Bei sehr kleinen Bauelementen wird dieser Kennwert durch Punchthrough verschlechtert. Bei NROM-Speicherzellen ist auf Grund der lokal gespeicherten Ladungen eine Degradation des subthreshold swings zu beobachten, [59].

Eine einfache Formel, bei der der Swing unabhängig von  $U_{GS}$  formuliert ist, findet man bei Liu et al., [40]:

$$S = \phi_t \ln 10 \left( 1 + \frac{\gamma}{2\sqrt{1, 5 \cdot \phi_F + U_{SB}}} \right) \tag{2.53}$$

Darüber hinaus entwickelt Liu, [40], ein Modell, das in Übereinstimmung mit den Ergebnissen von Tsividis, [69], den Swing als Funktion der Gate-Source-Spannung angibt, wobei dieser ein absolutes Minimum besitzt.

Der Swing kann auch in Abhängigkeit der flächenbezogenen Oxidkapazität,  $C'_{ox}$ , und der flächenbezogenen Kapazität der Verarmungszone,  $C'_{d}$ , angegeben werden,[19]:

$$S = \left(1 + \frac{C_d'}{C_{ox}'}\right) U_{th} \cdot \ln(10) \tag{2.54}$$

Zur Berücksichtigung von Kurzkanaleffekten haben Godoy et al. diese Formel erweitert:

$$S = \left(\frac{1}{\lambda_S} + \frac{C_d'}{C_{ox}'}\right) U_{th} \cdot \ln(10) \tag{2.55}$$

wobei  $\lambda_S$  durch einen unhandlichen Term gegeben ist, der für kleine Drain-Source-Spannungen vereinfacht werden kann zu:

$$\lambda_S \simeq 1 - \frac{1}{\cosh\left(\frac{L}{2l_S}\right)} \tag{2.56}$$

L ist die Kanallänge und  $l_S$  wird als typische Länge bezeichnet, für die gilt:

$$l_S = \sqrt{\frac{\epsilon_{Si} \cdot d_{ox} \cdot x_d}{\epsilon_{ox}}} \tag{2.57}$$

Aus dieser Erweiterung folgt, dass der Swing nicht nur von der Wannendotierung, sondern auch von der Kanallänge abhängt. Für kurze effektive Kanallängen nehmen die Werte für den Swing deutlich zu.

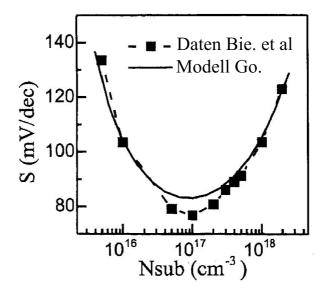

In Abbildung 2.15 ist der Swing über die Wannendotierung aufgetragen. Man sieht, dass er zu sehr hohen Werten der Dotierung hin ansteigt, dies folgt bereits aus Gleichung (2.53), da die Dotierung dort im Zähler über das  $\gamma$  stärker gewichtet ist, als im Nenner über  $\phi_F$ . Geht man zu sehr niedrigen Werten für die Dotierung, so zeigt der Transistor Kurzkanalverhalten. In diesem Bereich steigt der Wert für S auf Grund des Einflusses von  $\lambda_S$ . Es existiert also ein absolutes Minimum für den Swing.

Abbildung 2.15: subthreshold swing vs. Wannendotierung  $(N_{sub})$ ; Vergleich des Modells von Godoy,[19], mit den Daten von Biesemans et al.,[4], für einen MOS Transistor mit  $d_{ox} = 7,5nm$ , L = 250nm und  $U_{DS} = 0.1V$ , [19].

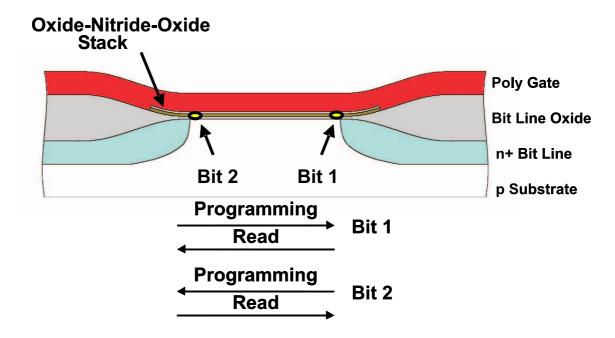

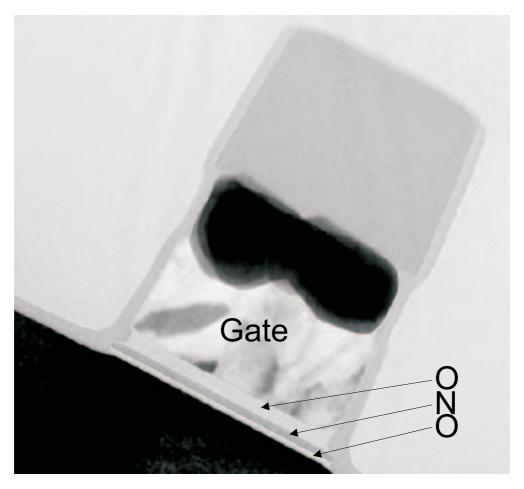

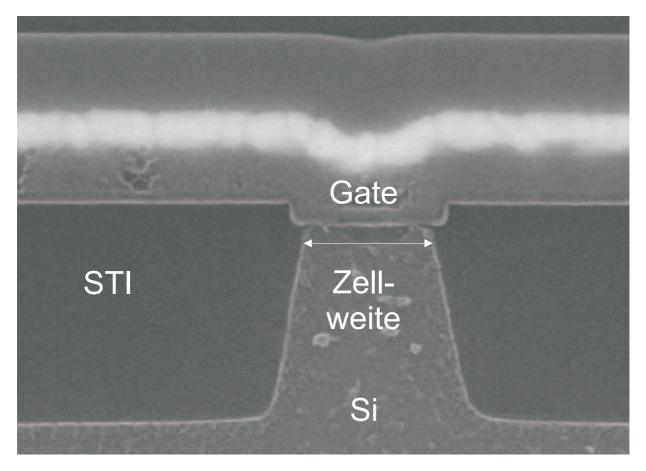

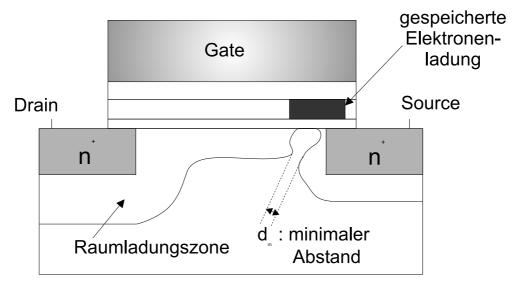

# 2.4 NROM-Speicherzelle

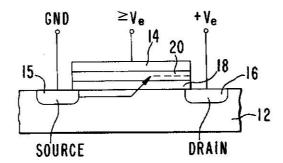

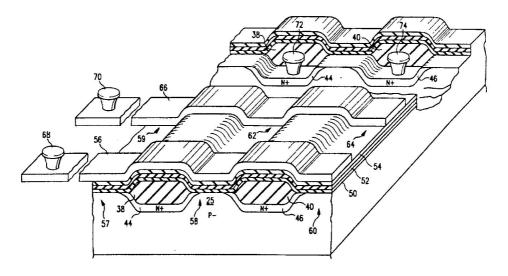

Die Grundstruktur der NROM-Zelle basiert auf einem n-Kanal MOSFET, wie er zuvor besprochen wurde. Der entscheidende Unterschied ist, dass das Gateoxid durch einen Oxid-Nitrid-Oxid Stapel (ONO) ersetzt wird. Hierdurch wird die Möglichkeit geschaffen, Ladungen zu speichern. Diese werden lokal im Nitrid gespeichert. Vorschläge zu Speicherbausteinen, die auf diesem Prinzip beruhen, sind bereits in den 70er Jahren zu finden. So ist bereits in dem United States Patent 4,173,766 von 1979 ein Bauelement zu finden, das mit dem hier beschriebenen Mechanismus arbeitet, siehe Abbildung 2.16.

Die Beweglichkeit der Ladungsträger im Nitrid ist sehr gering, sie können sich nicht lateral über die Kanallänge verteilen. Hierdurch ergibt sich ein wesentlicher Vorteil zu anderen Technologien im NVM (non volotile memory) Bereich. In einer NROM-Zelle können zwei physikalisch getrennte Bits pro Zelle gespeichert werden, dies ist schematisch in Abbildung 2.17 dargestellt, [14]. Die gespeicherten Ladungen ändern die Einsatzspannungen des

Abbildung 2.16: Frühe ONO-Speicherzelle, die Schichten mit den Zahlen 18, 20 und 14 bilden den ONO-Stapel; die anderen Zahlen sind hier nicht weiter von Bedeutung; [23].

Transistors. Dies wird zur Detektion des Speicherzustands ausgenutzt.

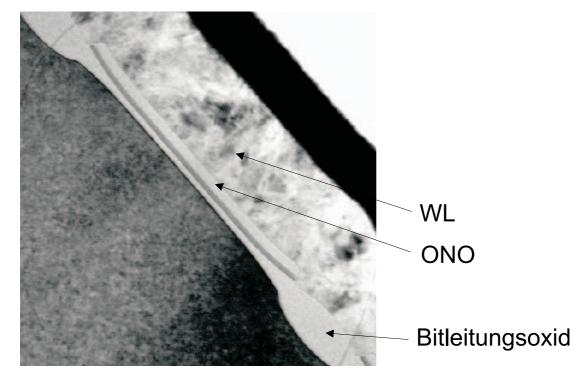

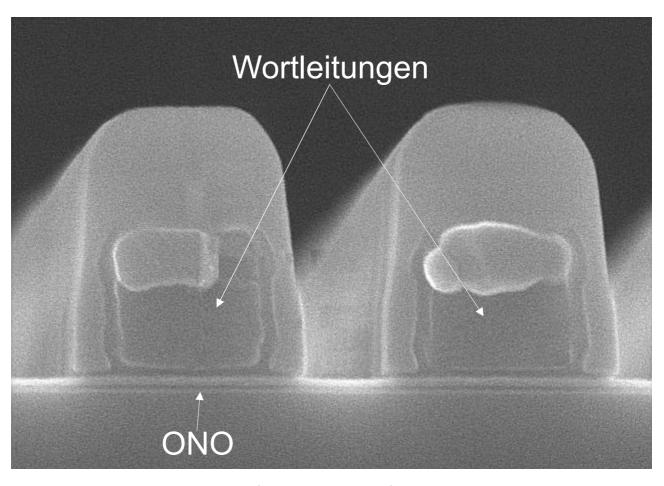

Hier ist eine herkömmliche NROM-Zelle abgebildet, das Wachsen eines Bitline-Oxids und die Biegung des ONO-Stapels am Rand sind nicht zwangsläufig bei einer NROM-Zelle vorhanden.

### 2.4.1 Schreiben, Lesen und Löschen

Wie aus Abbildung 2.17 leicht ersichtlich, ist die NROM-Zelle symmetrisch. Aus diesem Grund wird nur Bit 1 betrachtet, die Überlegungen gelten analog für Bit 2.

### Schreiben

Für das Schreiben eines Bits wird zuerst eine hohe positive Spannung am Gate angelegt (z.B.  $U_{GS} = 10V$ ). Durch diese Spannung wird ein Inversionskanal geöffnet. Nun wird an die Drain eine positive Spannung (z.B.  $U_{DS} = 5V$ ) angelegt. Hierdurch werden die Elektronen auf ihrem Weg zur Drain immer stärker beschleunigt. Auf dem letzten Stück der Strecke fällt der größte Teil der Spannung ab, hier bekommen die Elektronen so viel Energie, dass sie zu heißen Elektronen (CHE = channel hot electrons) werden und durch Stoßionisation Bindungen aufschlagen können. Die erzeugten Elektronen können die Potentialbarriere des Oxids überwinden und im Nitrid gespeichert werden. So wird eine Elektronenverteilung

Abbildung 2.17: Grundstruktur einer NROM-Speicherzelle

(siehe 2.17: Bit 1) erzeugt.

#### Lesen

Für das Lesen des nun geschriebenen Bits 1 wird der Transistor in entgegengesetzter Richtung betrieben (Source und Drain werden vertauscht). Die angelegten Spannungen sind sehr viel geringer (z.B.  $U_{GS}=3\ldots4.5V$  und  $U_{DS}=1.6V$ ). Dies ist aus zwei Gründen sofort klar; zum einen will man die Einsatzspannung messen, und zum anderen will man natürlich beim Lesen von Bit 1 nicht gleichzeitig Bit 2 schreiben. Durch eine derartige Messung wird die Einsatzspannung bestimmt, welche sehr sensitiv auf die eingeschossene Elektronenladung (Bit 1) ist. Da man beide Ladungen getrennt detektieren will, wird - wie oben beschrieben - eine Source-Drain-Spannung von ca.  $U_{DS}=1.6V$  verwendet. Hierdurch wird die Verarmungszone an der neuen Drain vergrößert und bei der Messung der Transferkurve haben die gespeicherten Elektronen auf dieser Seite nur einen geringen Einfluss, [42]. Es ist leicht möglich, durch das Programmieren die Einsatzspannung um 2V zu erhöhen.

### Löschen

Gelöscht wird eine Elektronenladung durch das Einschiessen von Löchern. Hierzu wird eine negative Spannung am Gate angelegt (z.B.  $U_{GS} = -10V$ ), und zudem wird die Drainspannung erhöht ( $U_{DS} = 4...6V$ ). Dies führt drainseitig zu einer sehr starken Bandverbiegung, es werden Löcher generiert und beschleunigt. Gelangen diese in das Nitrid, so kompensieren sie die vorhandene Elektronenladung und somit wird die Einsatzspannung des Transistors wieder auf den Ausgangswert gesenkt. Das Bit ist wieder gelöscht. Ein guter räumlicher Überlapp der Löcher und Elektronen wird zumindest am Beginn des Löschens durch das lokale Feld der Elektronen begünstigt, es liegt eine Selbstjustierung vor.

# Kapitel 3

# Zellkonzepte und Modellbildung für NROM-Zellen

In diesem Kapitel werden zwei grundlegend unterschiedliche Konzepte für den Aufbau einer NROM-Speicherzelle vorgestellt. Zuerst wird ein "konventionelles" Konzept vorgestellt. Konventionell bezieht sich in diesem Zusammenhang darauf, dass dieses Konzept bereits für Produkte, die auf dem Markt erhältlich sind, Verwendung findet und in einer Reihe von Publikationen behandelt wird, [5],[13],[27],[45].

Das zweite Konzept ist ein neuartiges Konzept, das von Dr. Josef Willer, [74], angestoßen wurde. Die Zellen werden seitlich durch STI begrenzt. Dies führt zu einem anderen Verhalten der Zellen als beim konventionellen Konzept.

Im Anschluss an die Vorstellung der beiden Zellkonzepte, folgt eine Abhandlung zur Modellbildung der NROM-Zelle, die nicht konzeptgebunden ist. Hier sollen Modelle behandelt werden, welche das Verständnis zu physikalischen Vorgängen in der NROM-Zelle vertiefen, respektive später für die Erklärung von Verlustmechanismen herangezogen werden können. Somit wird die Grundlage für eine besseres Verständnis der experimentellen Resultate im nachfolgenden Kapitel geschaffen.

# 3.1 Konventionelles Konzept (C-Konzept)

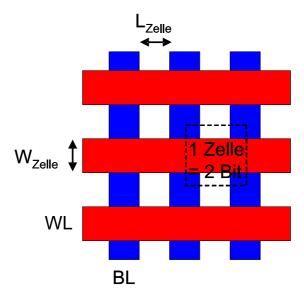

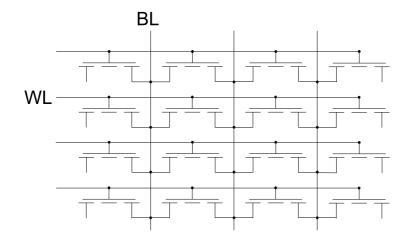

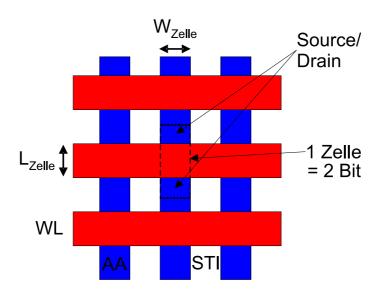

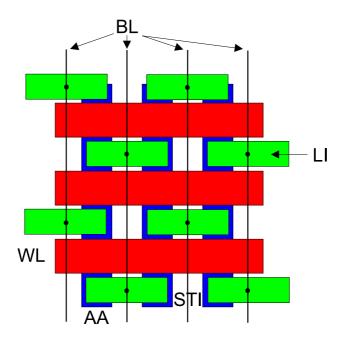

Im Verlaufe dieser Arbeit wird dieses Konzept mit CC (conventional concept) abgekürzt. Zuerst betrachten wir den prinzipiellen Aufbau eines Zellenfeldes nach diesem Konzept. Eine solche Architektur ist in Abbildung 3.1 zu sehen, sie ist aus der Literatur bekannt, [5], [13].

Abbildung 3.1: Struktur der Zellanordnung im C-Konzept; WL = Wortleitung, BL = Bitleitung,  $W_{Zelle}$  = gezeichnete Weite einer Zelle,  $L_{Zelle}$  = gezeichnete Länge einer Zelle